# **Vision HDL Toolbox™**

User's Guide

# MATLAB®

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

**7**

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Vision HDL Toolbox™ User's Guide

© COPYRIGHT 2015-2021 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

#### **Revision History**

| March 2015     | Online only | New for Version 1.0 (Release R2015a)     |

|----------------|-------------|------------------------------------------|

| September 2015 | Online only | Revised for Version 1.1 (Release R2015b) |

| March 2016     | Online only | Revised for Version 1.2 (Release R2016a) |

| September 2016 | Online only | Revised for Version 1.3 (Release R2016b) |

| March 2017     | Online only | Revised for Version 1.4 (Release R2017a) |

| September 2017 | Online only | Revised for Version 1.5 (Release R2017b) |

| March 2018     | Online only | Revised for Version 1.6 (Release 2018a)  |

| September 2018 | Online only | Revised for Version 1.7 (Release 2018b)  |

| March 2019     | Online only | Revised for Version 1.8 (Release 2019a)  |

| September 2019 | Online only | Revised for Version 2.0 (Release 2019b)  |

| March 2020     | Online only | Revised for Version 2.1 (Release 2020a)  |

| September 2020 | Online only | Revised for Version 2.2 (Release 2020b)  |

| March 2021     | Online only | Revised for Version 2.3 (Release 2021a)  |

| September 2021 | Online only | Revised for Version 2.4 (Release 2021b)  |

|                |             |                                          |

# **Contents**

| Streaming Pixel Inter                                                                                   | tac      |

|---------------------------------------------------------------------------------------------------------|----------|

|                                                                                                         |          |

| Streaming Pixel Interface                                                                               | 1-2      |

| What Is a Streaming Pixel Interface?                                                                    | 1-       |

| How Does a Streaming Pixel Interface Work?                                                              | 1-       |

| Why Use a Streaming Pixel Interface?                                                                    | 1-<br>1- |

| Pixel Stream Conversion Using Blocks and System Objects Timing Diagram of Single Pixel Serial Interface | 1-<br>1- |

| Timing Diagram of Multipixel Serial Interface                                                           | 1-       |

| ilter Multipixel Video Streams                                                                          | 1-       |

| AultiPixel-MultiComponent Video Streaming                                                               | 1-1      |

| Pixel Control Bus                                                                                       | 1-2      |

| Pixel Control Structure                                                                                 | 1-2      |

| Convert Camera Control Signals to pixelcontrol Format                                                   | 1-2      |

| Integrate Vision HDL Blocks into Camera Link System                                                     | 1-2      |

| HDL-Optimized Algorithm De                                                                              | sig      |

|                                                                                                         |          |

| Configure Blanking Intervals                                                                            | 2-<br>2- |

| Edge Padding                                                                                            | 2-       |

| Increase Throughput with Padding None                                                                   | 2-1      |

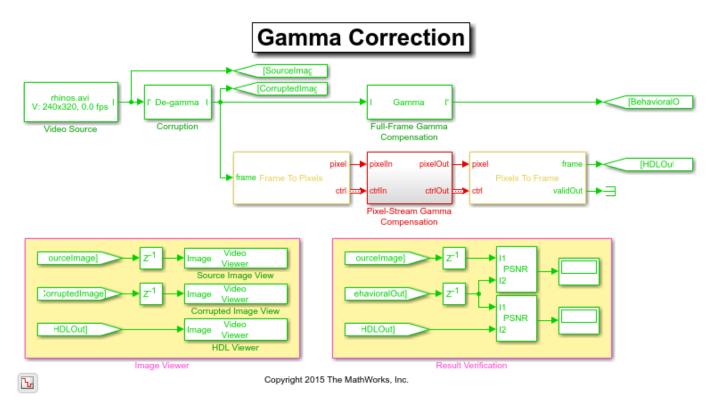

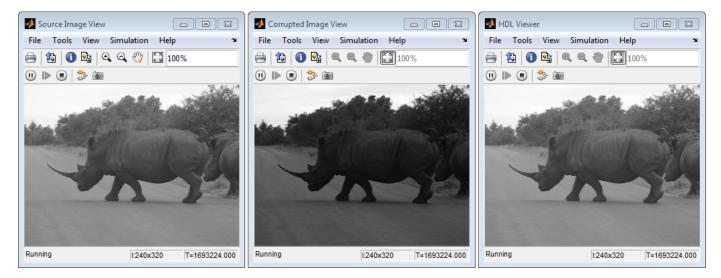

| Gamma Correction                                                                                        | 2-1      |

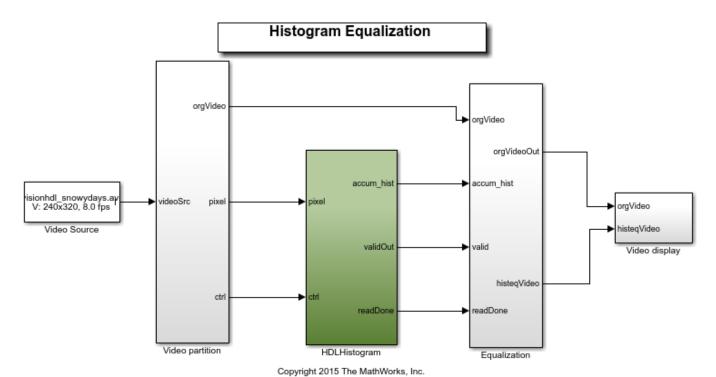

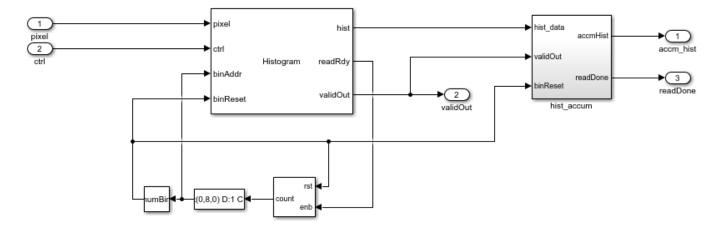

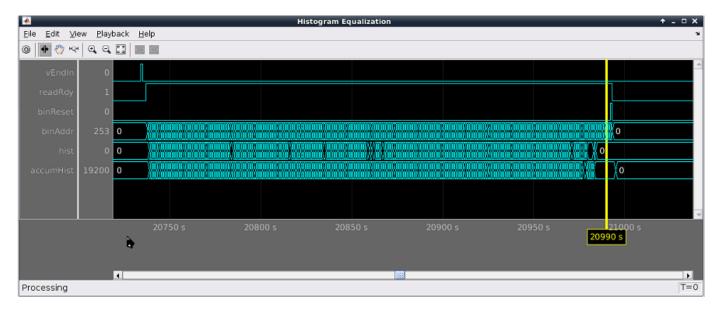

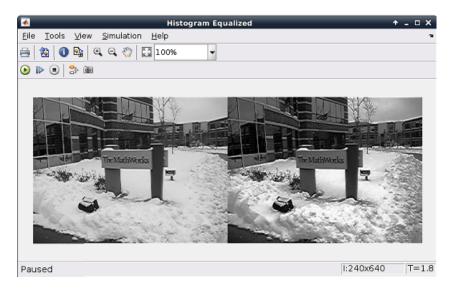

| Histogram Equalization                                                                                  | 2-2      |

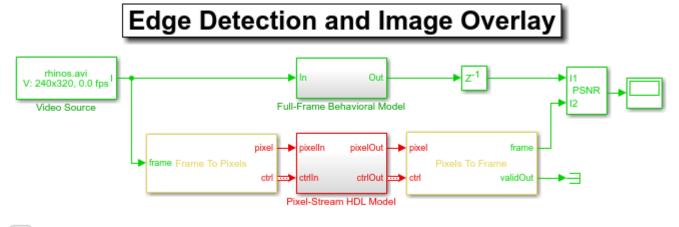

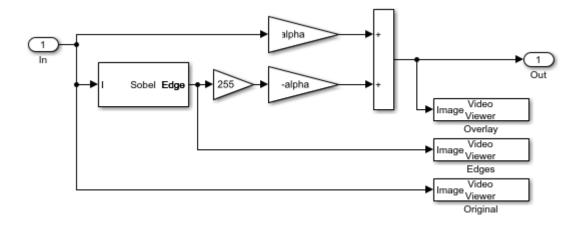

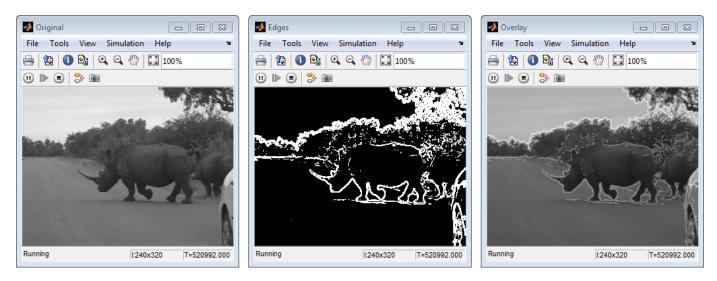

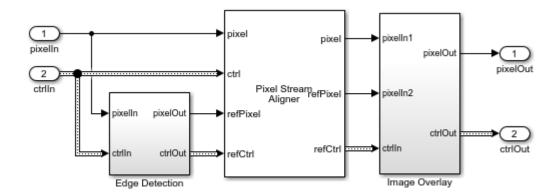

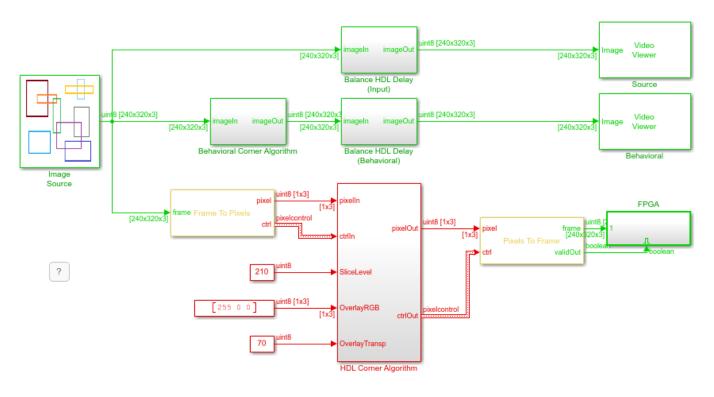

| Edge Detection and Image Overlay                                                                        |          |

| Edge Detection and Image Overlay with Impaired Frame                                                    | 2-2      |

|                                                                                                         | 2-2      |

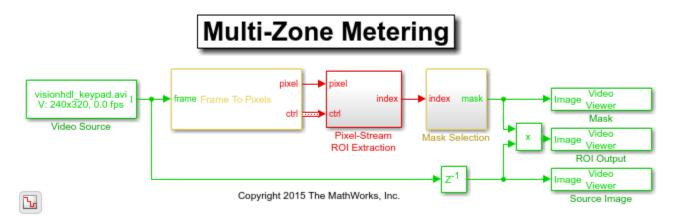

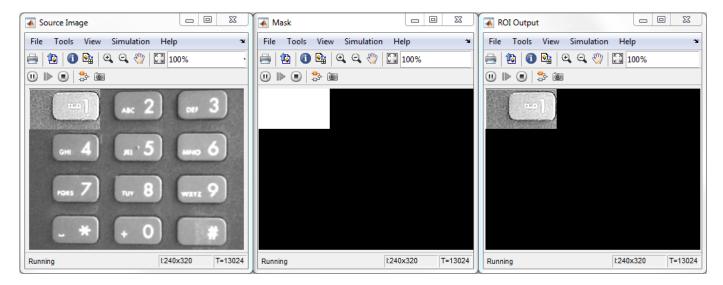

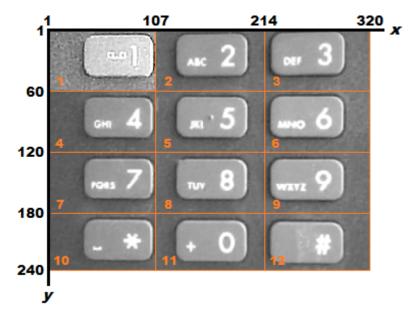

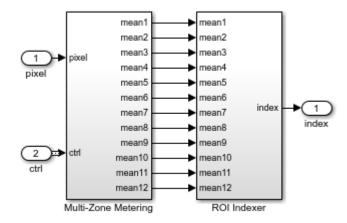

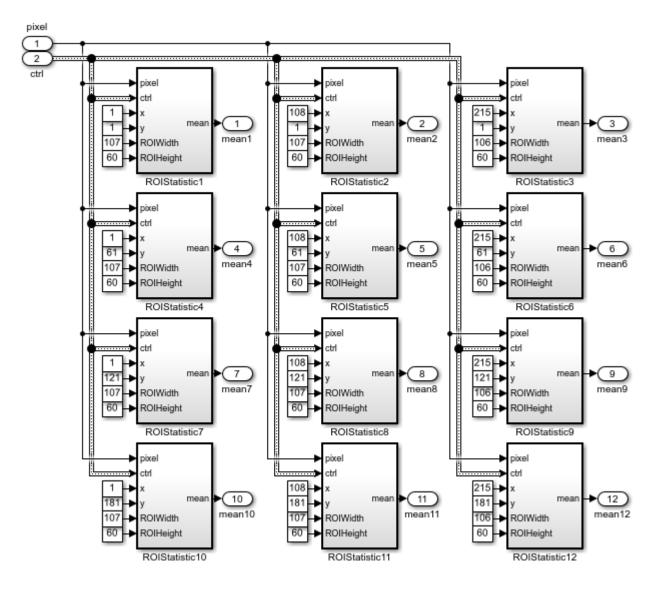

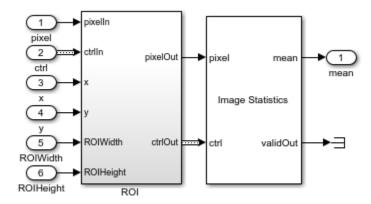

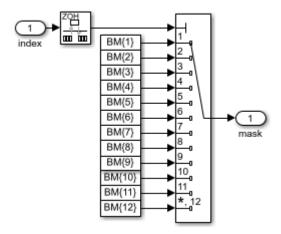

|            | Multi-Zone Metering                                                       | 2-41  |

|------------|---------------------------------------------------------------------------|-------|

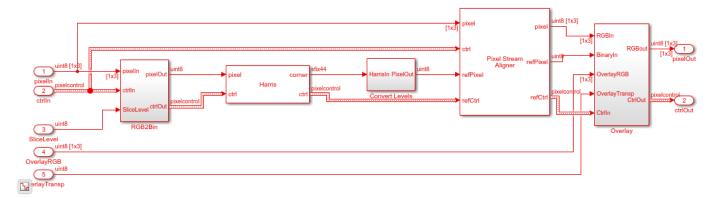

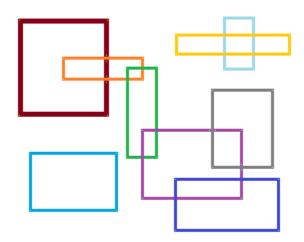

|            | Harris Corner Detection                                                   | 2-48  |

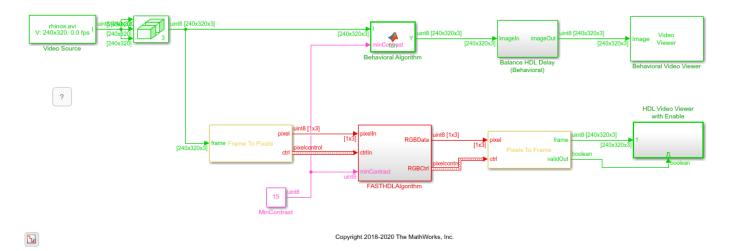

|            | FAST Corner Detection                                                     | 2-53  |

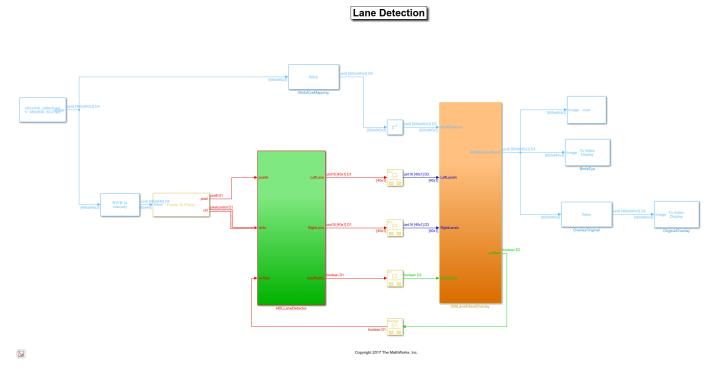

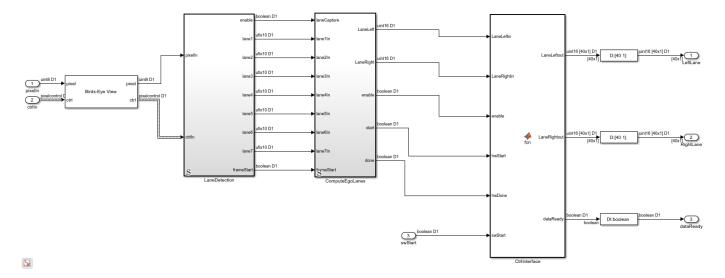

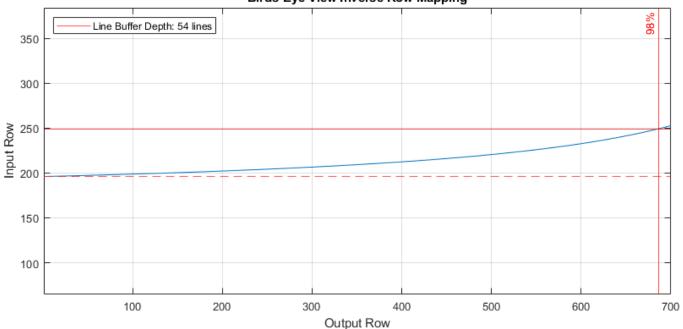

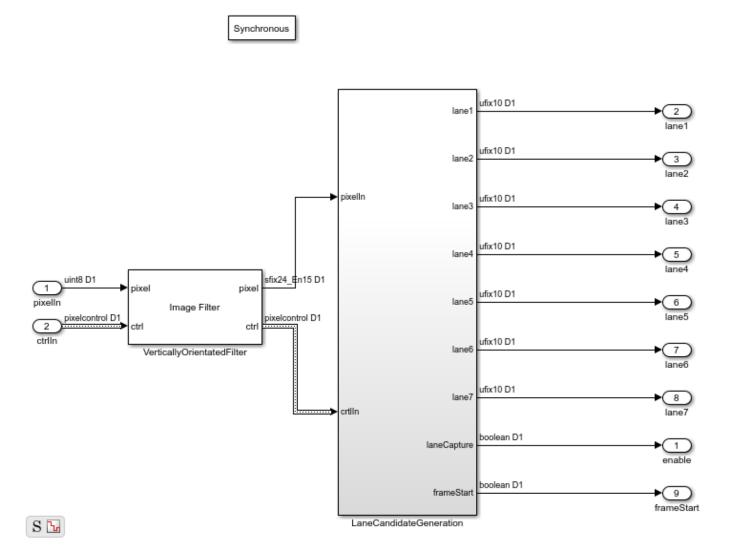

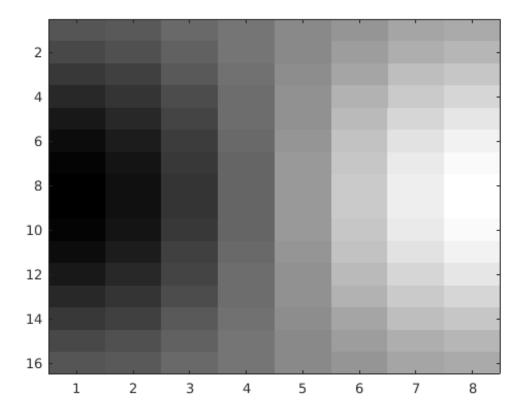

|            | Lane Detection                                                            | 2-60  |

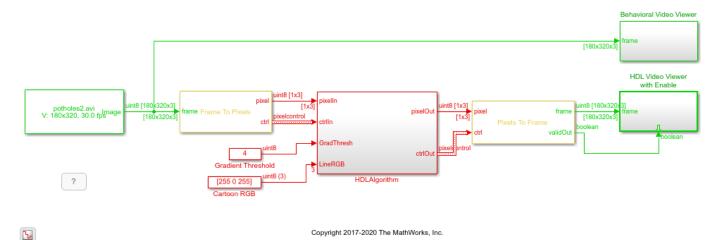

|            | Generate Cartoon Images Using Bilateral Filtering                         | 2-77  |

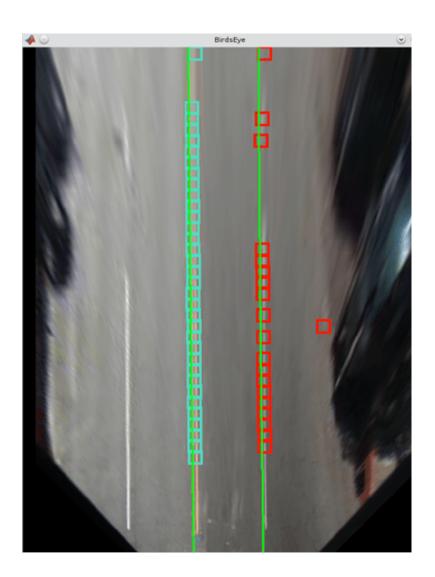

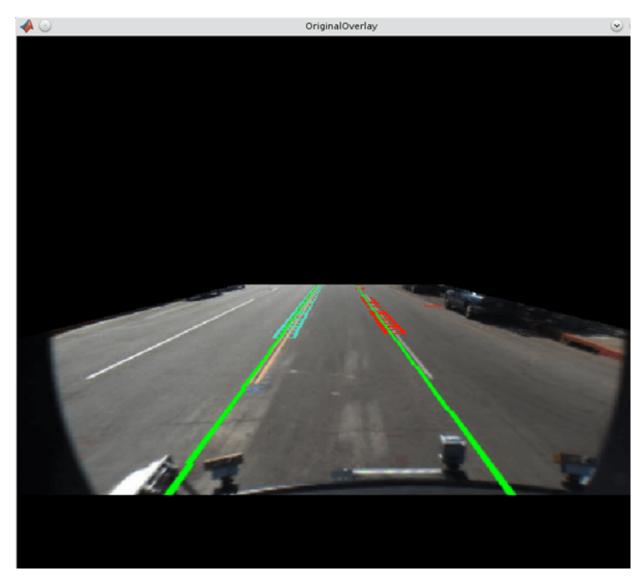

|            | Pothole Detection                                                         | 2-82  |

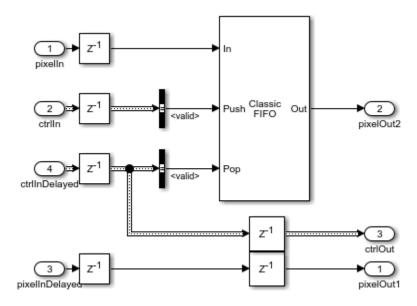

|            | Buffer Bursty Data Using Pixel Stream FIFO Block                          | 2-95  |

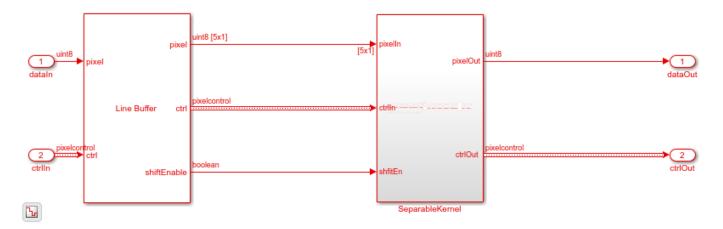

|            | Using the Line Buffer to Create Efficient Separable Filters               | 2-99  |

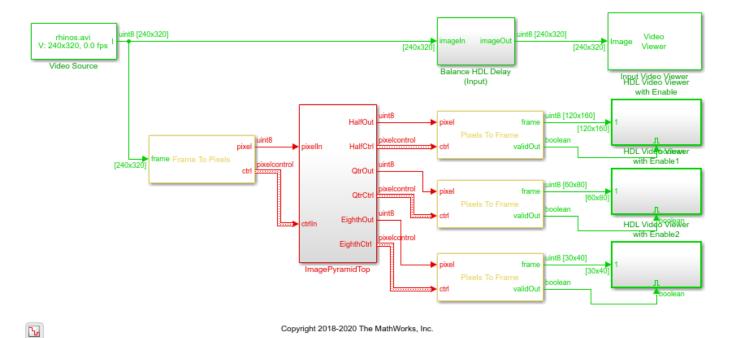

|            | Image Pyramid                                                             | 2-108 |

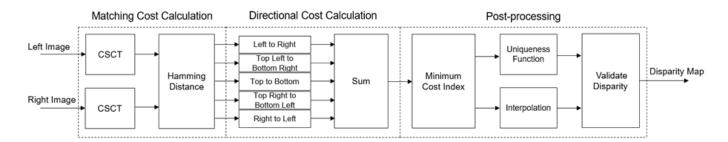

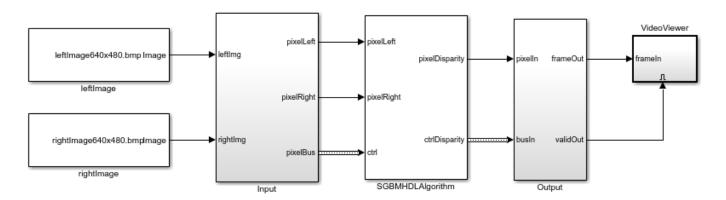

|            | Stereo Disparity Using Semi-Global Block Matching                         | 2-112 |

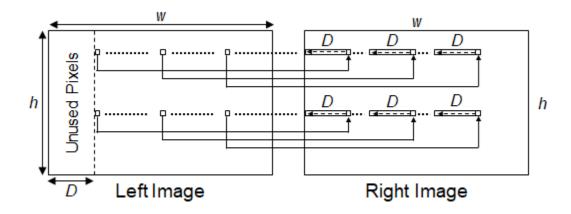

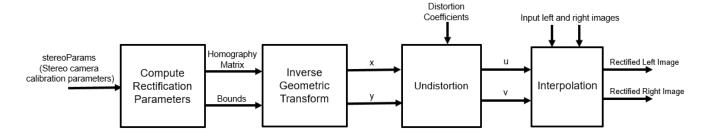

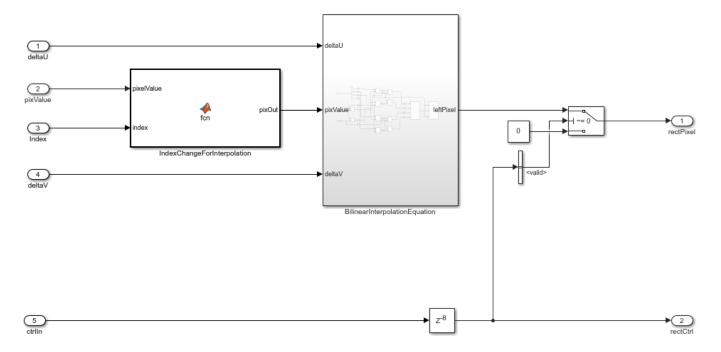

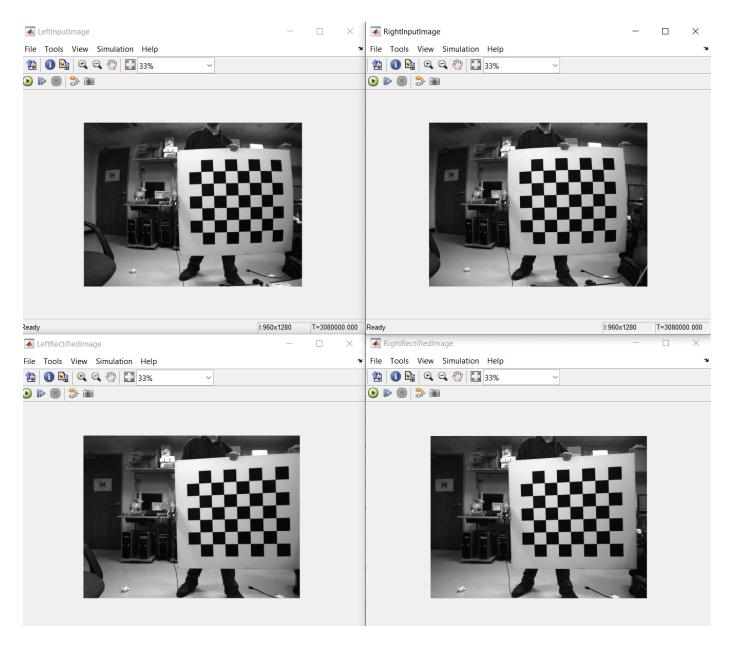

|            | Stereo Image Rectification                                                | 2-124 |

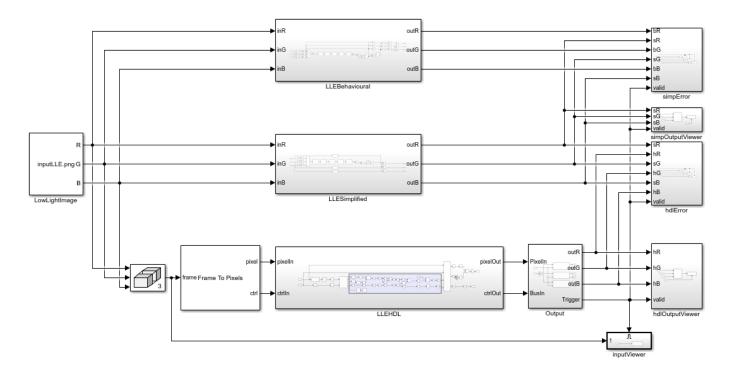

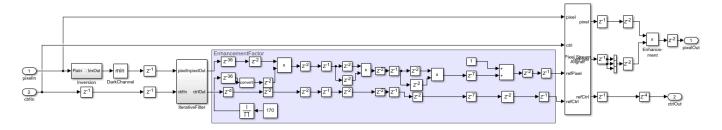

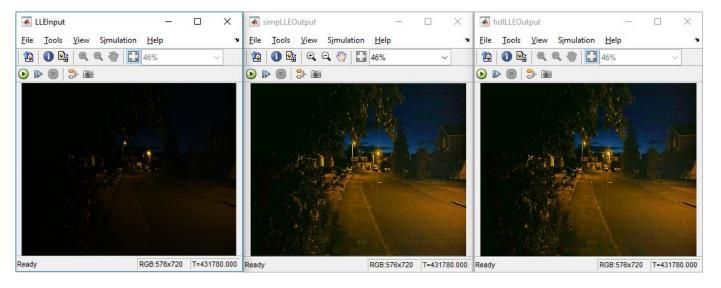

|            | Low Light Enhancement                                                     | 2-134 |

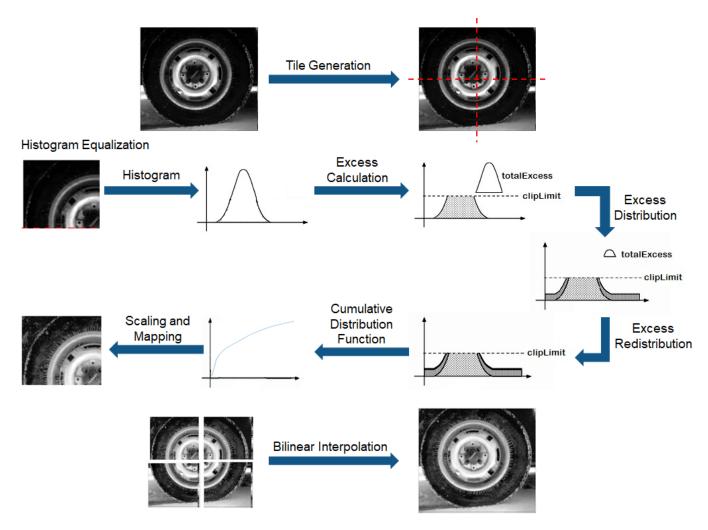

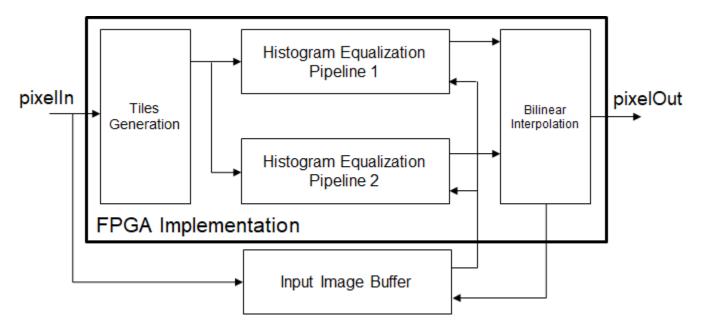

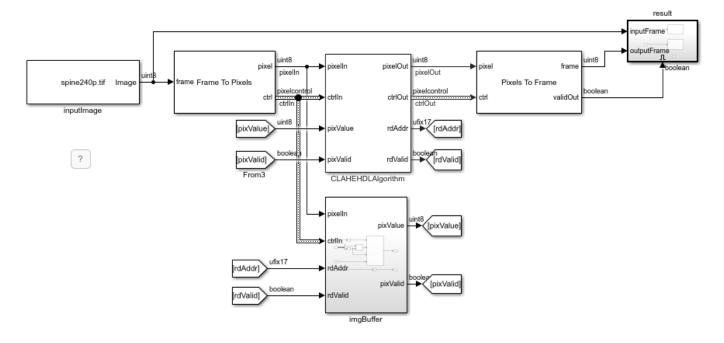

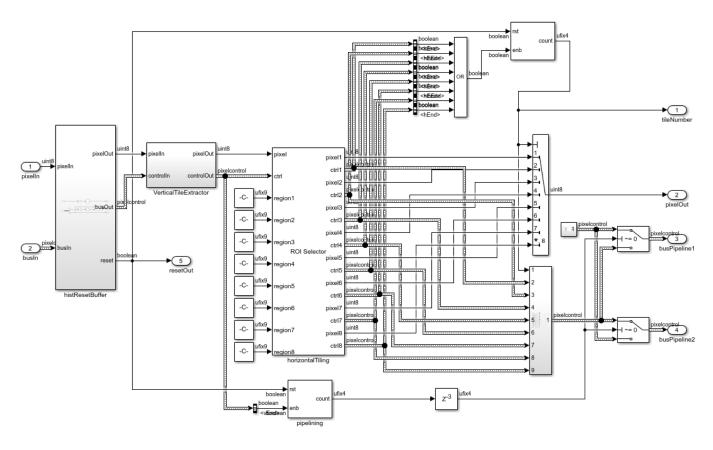

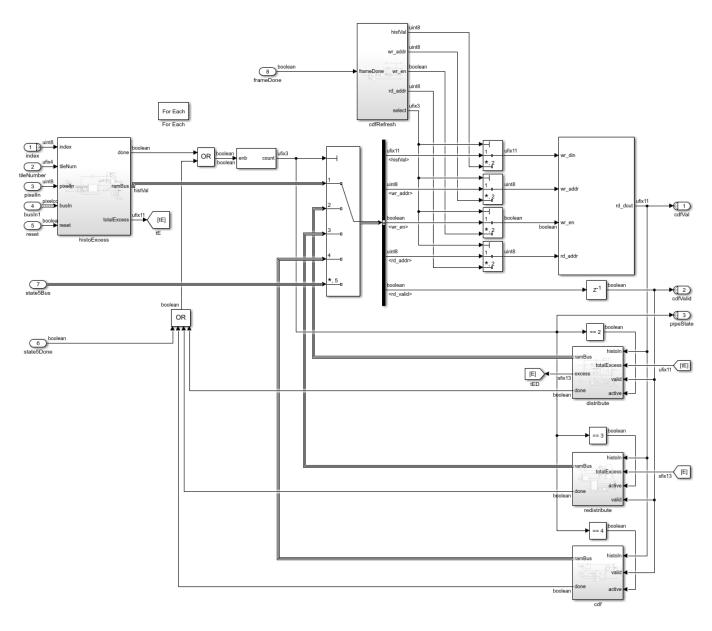

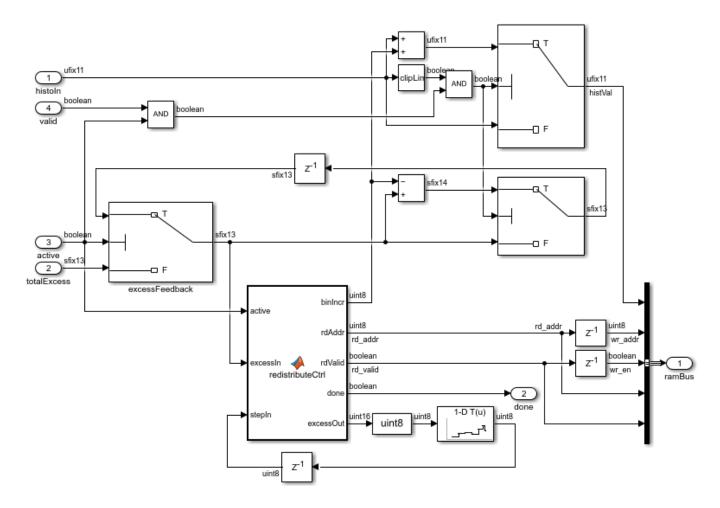

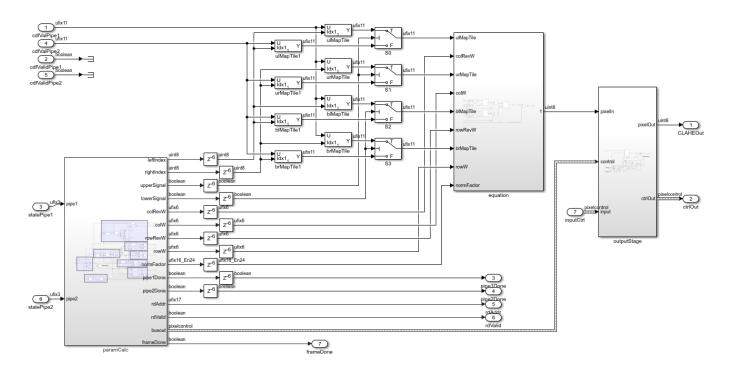

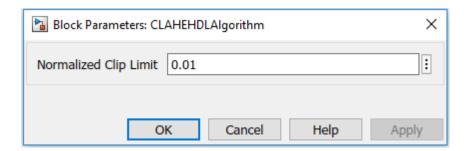

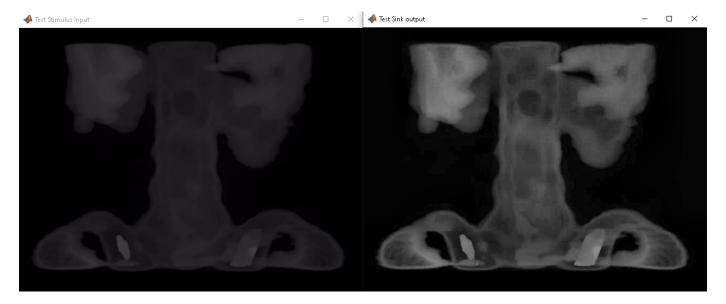

|            | Contrast Limited Adaptive Histogram Equalization                          | 2-140 |

|            | Image Resize                                                              | 2-151 |

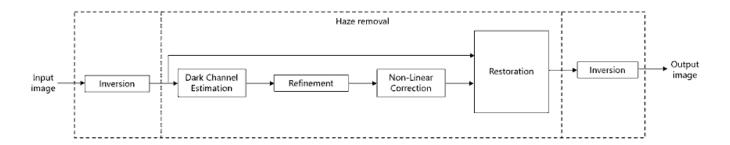

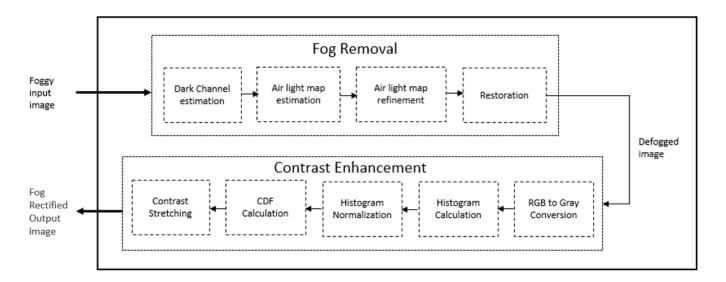

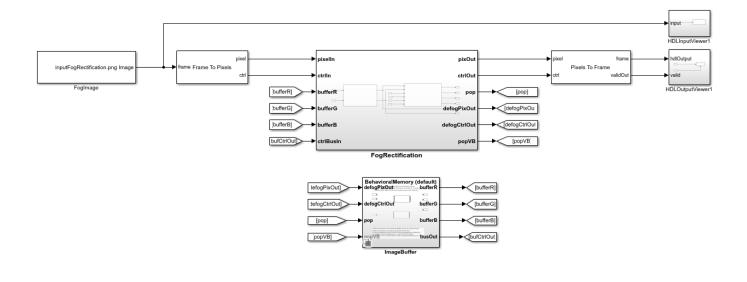

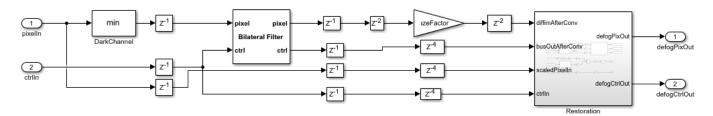

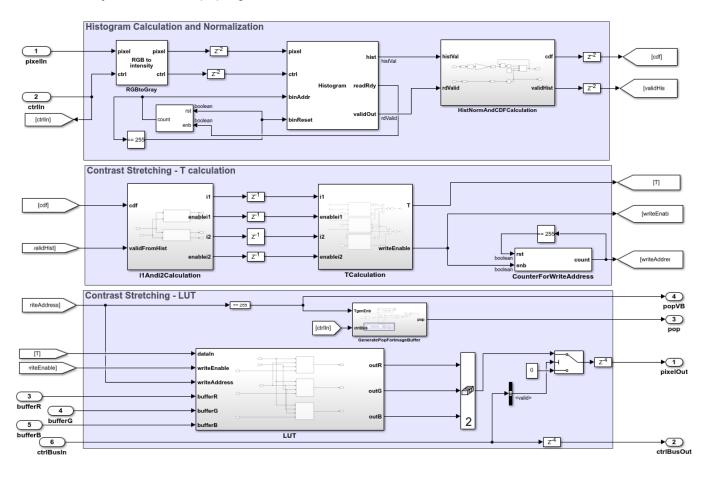

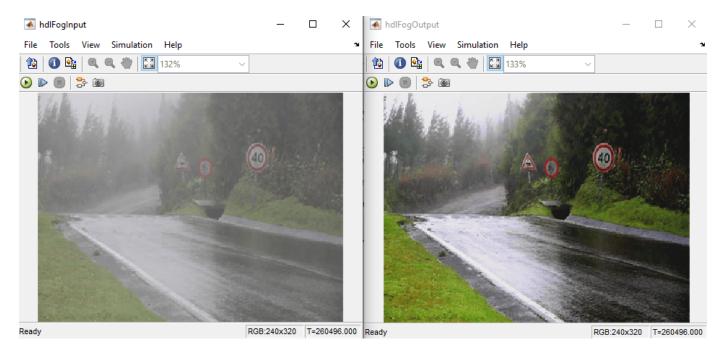

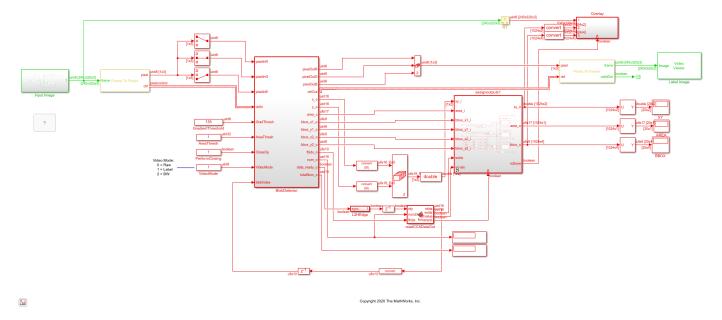

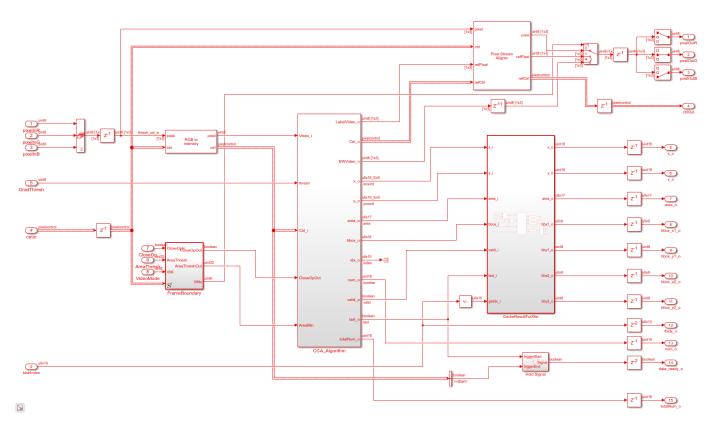

|            | Fog Rectification                                                         | 2-158 |

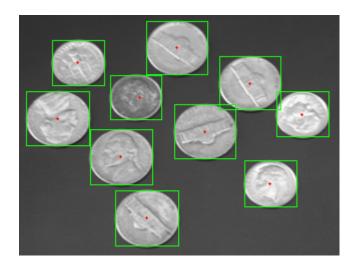

|            | Blob Analysis                                                             | 2-165 |

|            | Pixel-Streaming Design in MATLAB                                          | 2-171 |

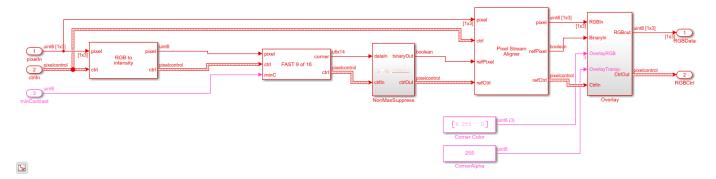

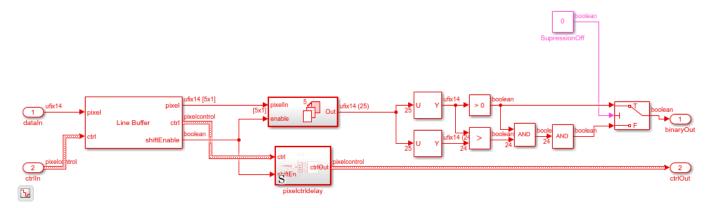

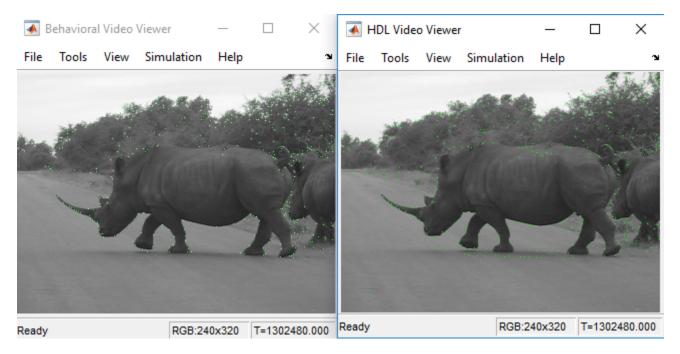

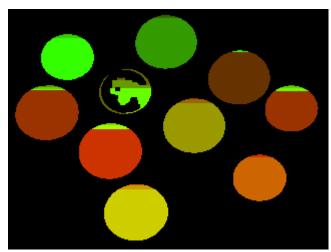

|            | Enhanced Edge Detection from Noisy Color Video                            | 2-173 |

| <b>3</b> □ | Code Generation and Deploy                                                | ment  |

| <b>J</b>   | Accelerate a MATLAB Design with MATLAB Coder                              | 3-2   |

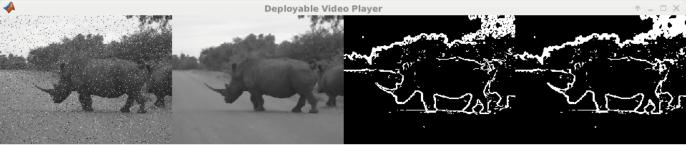

|            | HDL Code Generation from Vision HDL Toolbox  What Is HDL Code Generation? |       |

|            | Blocks and System Objects Supporting HDL Code Generation  Blocks          | 3-5   |

|            | Generate HDL Code from Simulink  Introduction  Prepare Model                                                             | 3-7<br>3-7<br>3-7    |

|------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|

|            | Generate HDL Code                                                                                                        | 3-7<br>3-7           |

|            | Generate HDL Code from MATLAB  Create an HDL Coder Project  Generate HDL Code                                            | 3-8<br>3-8<br>3-8    |

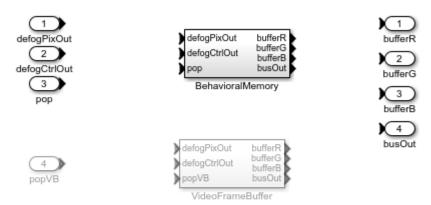

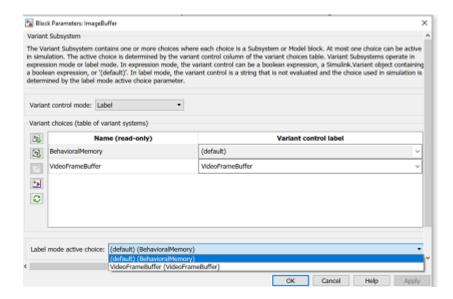

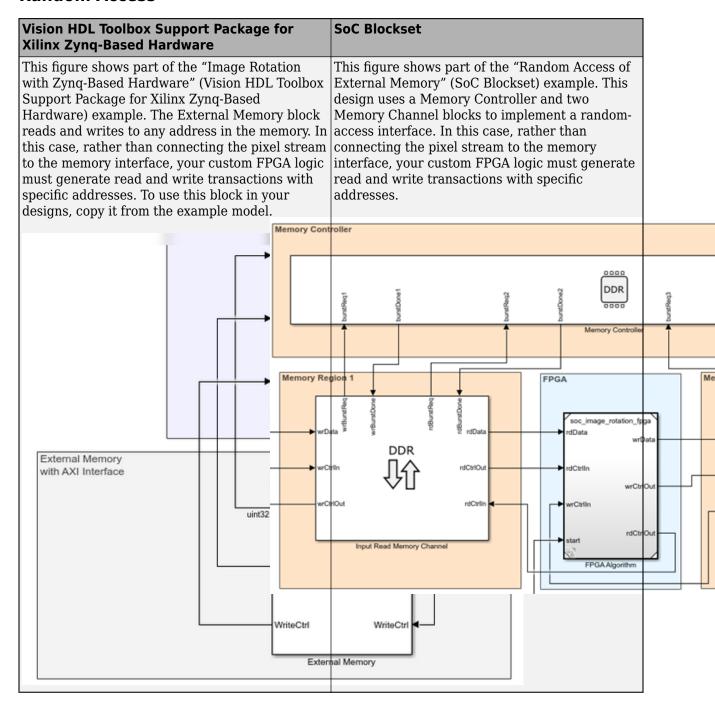

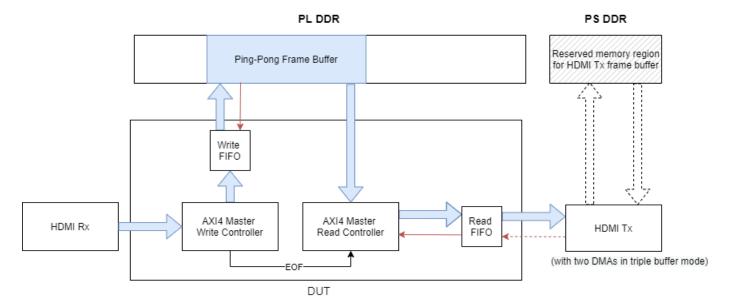

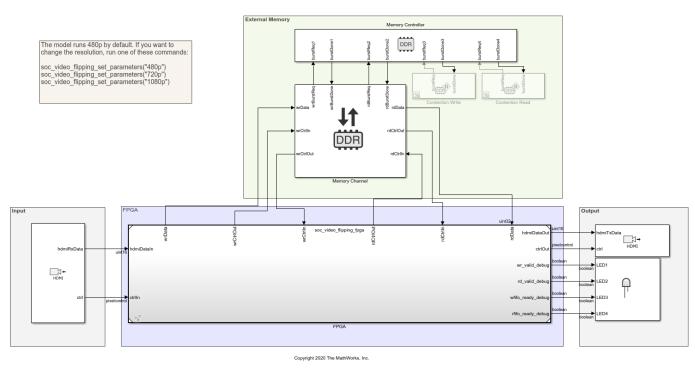

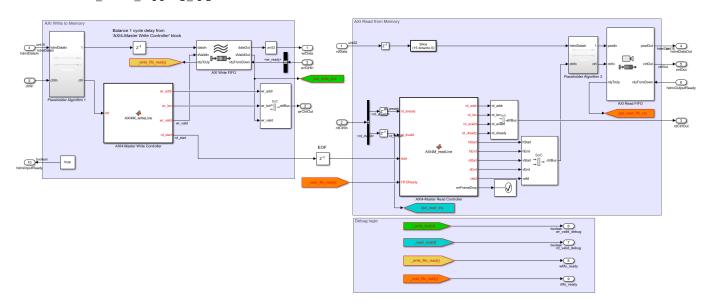

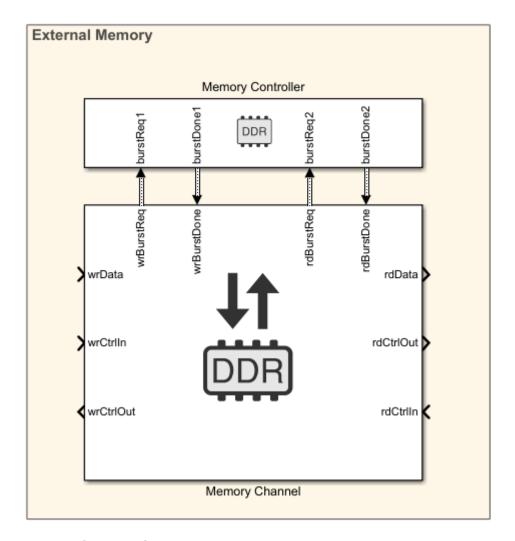

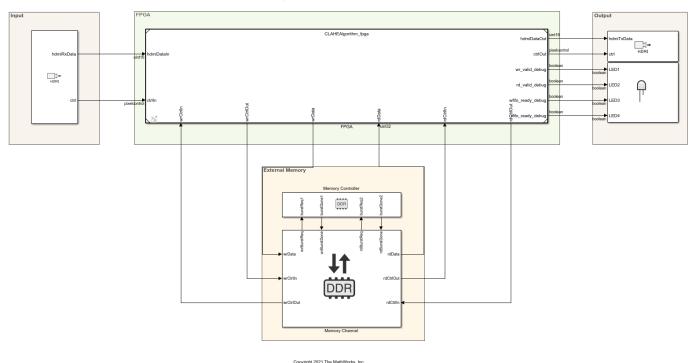

|            | Modeling External Memory  Frame Buffer                                                                                   | 3-10<br>3-11<br>3-12 |

|            | Vertical Video Flipping Using External Memory                                                                            | 3-14                 |

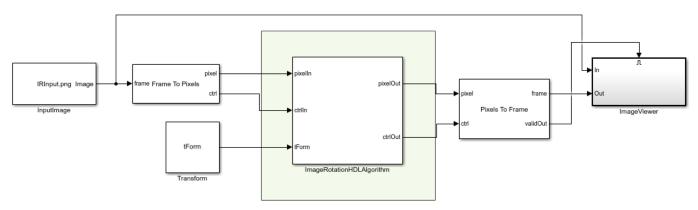

|            | Rotate Image by Small Acute Angle                                                                                        | 3-22                 |

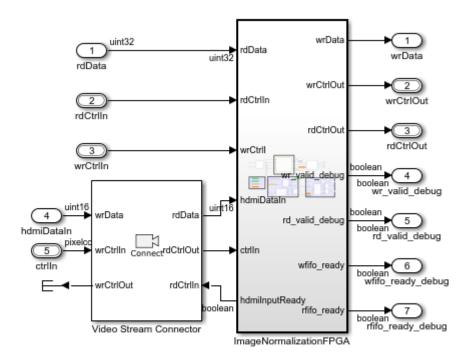

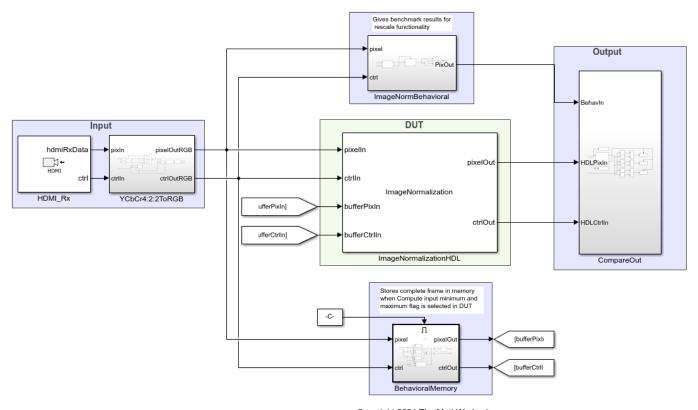

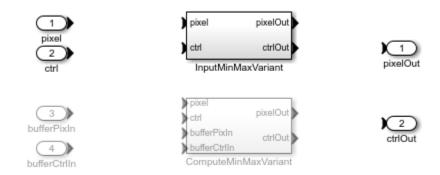

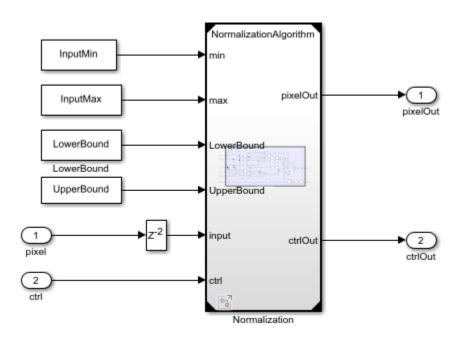

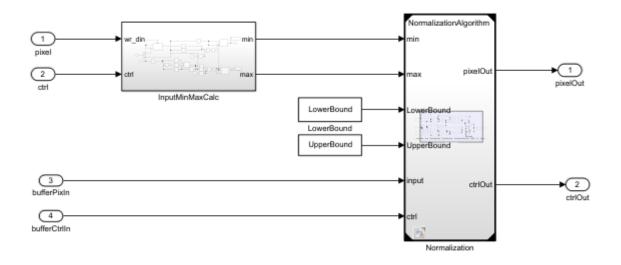

|            | Image Normalization Using External Memory                                                                                | 3-31                 |

|            | Contrast Limited Adaptive Histogram Equalization with External Memory                                                    | 3- <b>4</b> 3        |

|            | HDL Cosimulation                                                                                                         | 3-53                 |

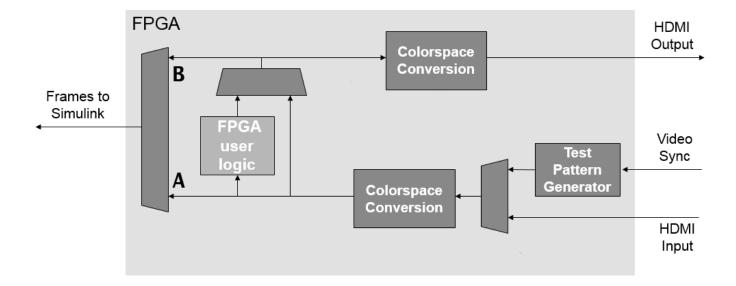

|            | FPGA-in-the-Loop                                                                                                         | 3-54                 |

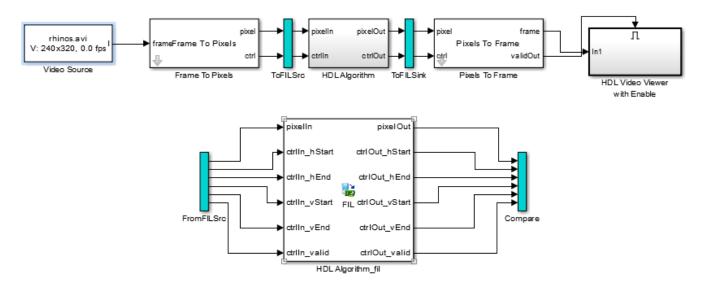

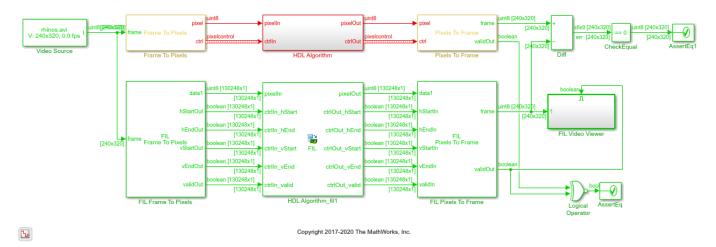

|            | FPGA-in-the-Loop Simulation with Vision HDL Toolbox Blocks                                                               | 3-54                 |

|            | FPGA-in-the-Loop Simulation with Multipixel Streaming FPGA-in-the-Loop Simulation with Vision HDL Toolbox System Objects | 3-55<br>3-57         |

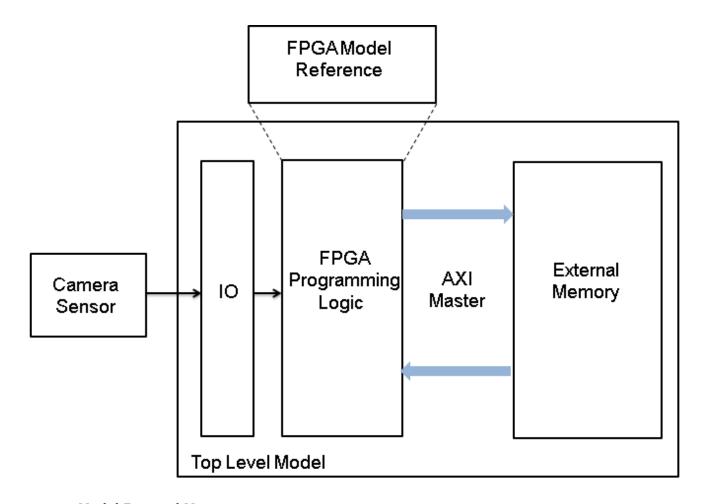

|            | Prototype Vision Algorithms on Zyng-Based Hardware                                                                       | 3-59                 |

|            | Video Capture                                                                                                            | 3-59                 |

|            | Reference Design                                                                                                         | 3-59<br>3-60         |

| <b>4</b> [ | Block Reference Exam                                                                                                     | ples                 |

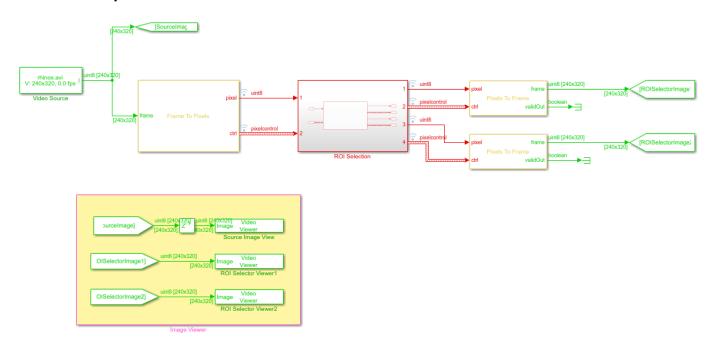

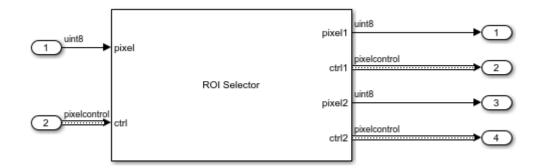

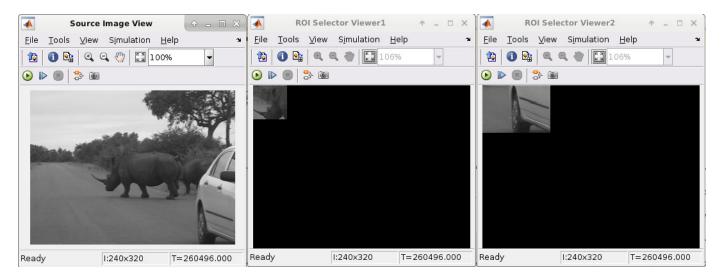

| -          | Select Region of Interest                                                                                                | 4-2                  |

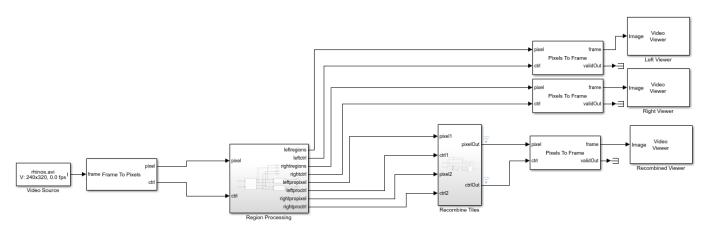

|            | Select Regions for Vertical Reuse                                                                                        | 4-6                  |

|            | Construct a Filter Using Line Buffer                                                                                     | 4-10                 |

|            | Convert RGB Image to YCbCr 4:2:2 Color Space                                                                             | 4-12                 |

|            | Compute Negative Image                                                                                                   | 4-14                 |

|            | Adapt Image Filter Coefficients from Frame to Frame                                                                      | 4-15                 |

|            | rampo imago i mor cocarciones irom i i ume to i i ume                                                                    | 110                  |

|   |   |   | L |

|---|---|---|---|

|   | 7 | ١ |   |

| 1 |   | ı |   |

|   |   |   |   |

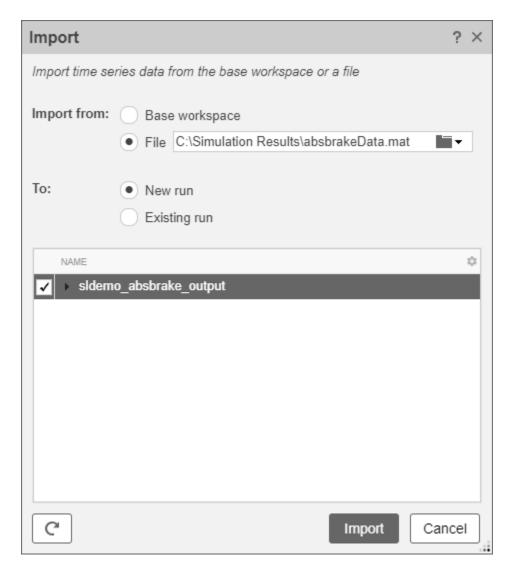

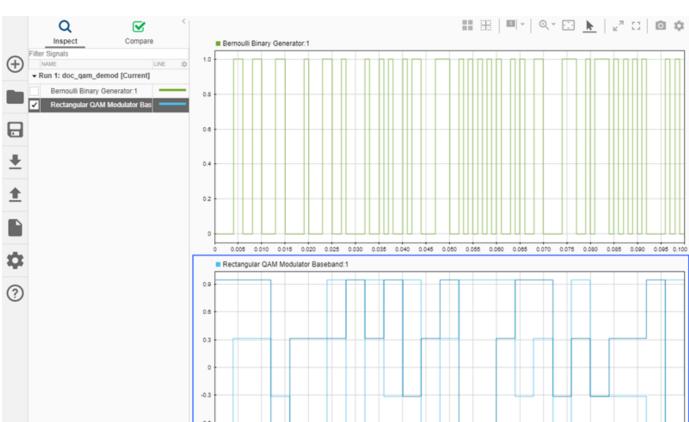

| View Data in the Simulation Data Inspector                                                         |            |

|----------------------------------------------------------------------------------------------------|------------|

| View Logged Data                                                                                   |            |

| View Complex Data                                                                                  |            |

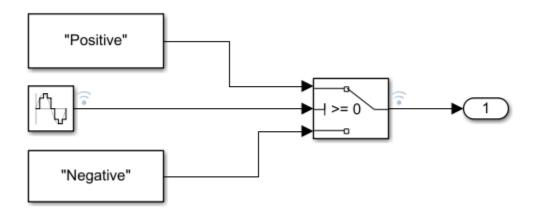

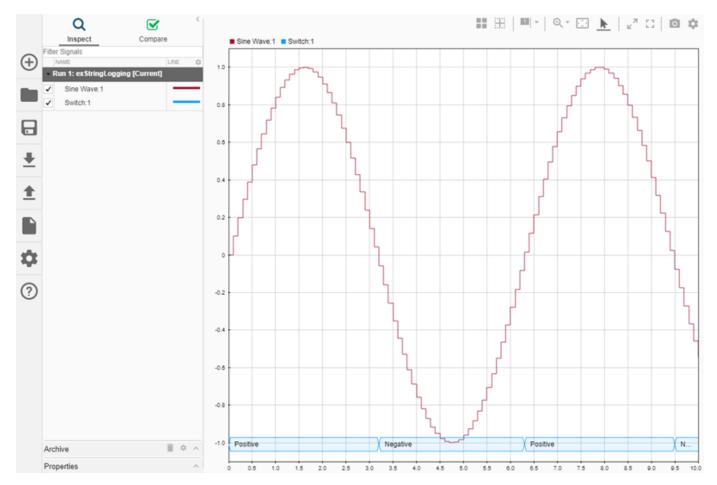

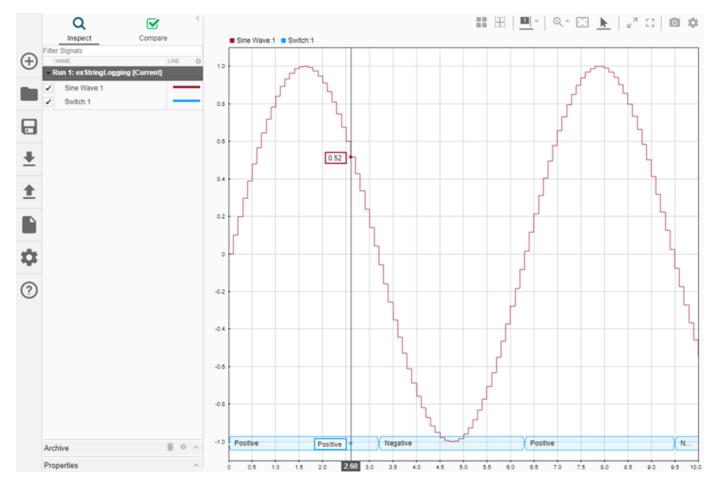

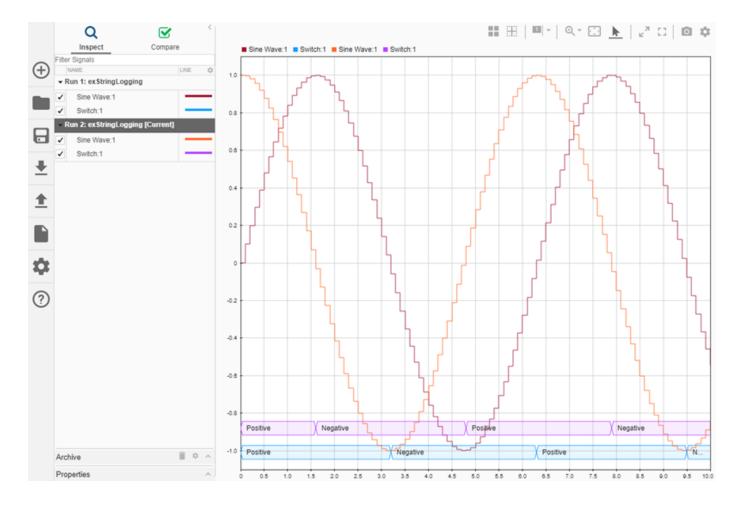

| View String Data                                                                                   |            |

| View Frame-Based Data 5                                                                            |            |

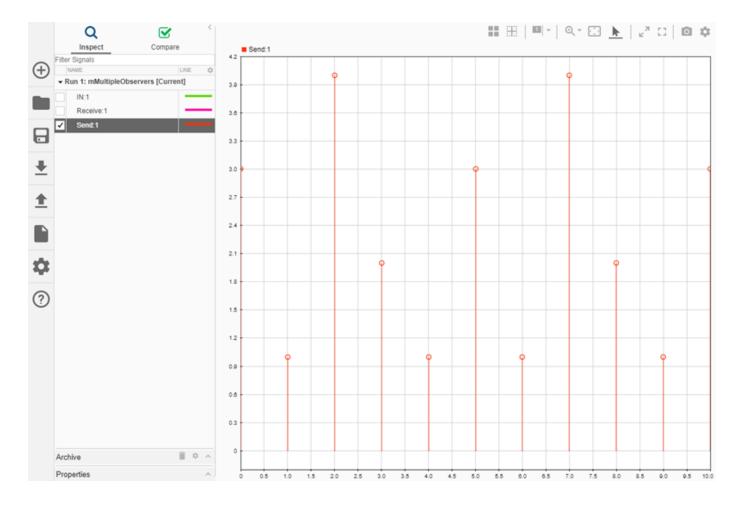

| View Event-Based Data                                                                              | <b>-</b> g |

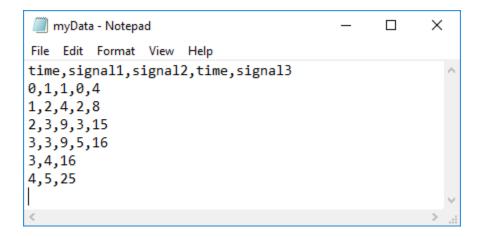

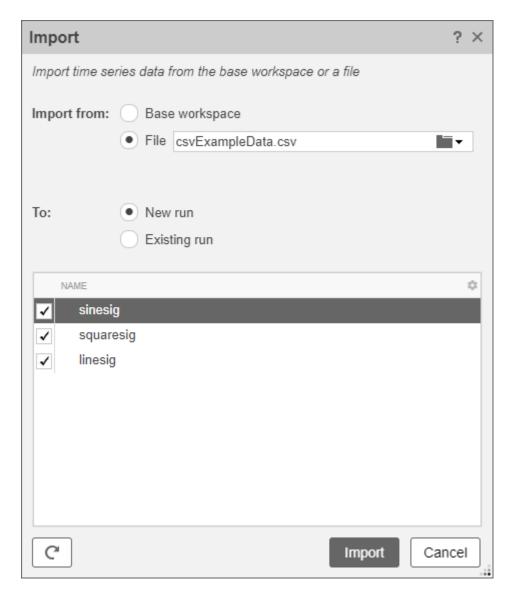

| Import Data from a CSV File into the Simulation Data Inspector 5-1                                 | I 1        |

| Basic File Format                                                                                  |            |

| Multiple Time Vectors                                                                              | 11         |

| Signal Metadata                                                                                    |            |

| Import Data from a CSV File 5-1                                                                    | 13         |

| Microsoft Excel Import, Export, and Logging Format 5-1                                             | 16         |

| Basic File Format 5-1                                                                              | 16         |

| Multiple Time Vectors                                                                              |            |

| Signal Metadata 5-1                                                                                |            |

| User-Defined Data Types                                                                            |            |

| Complex, Multidimensional, and Bus Signals         5-2           Function-Call Signals         5-2 |            |

| Function-Call Signals                                                                              |            |

| Multiple Runs                                                                                      |            |

| Tutapo Tuta                                                                                        |            |

| Configure the Simulation Data Inspector                                                            | 24         |

| Logged Data Size and Location                                                                      |            |

| Archive Behavior and Run Limit                                                                     |            |

| Incoming Run Names and Location                                                                    |            |

| Signal Metadata to Display                                                                         |            |

| Signal Selection on the Inspect Pane                                                               |            |

| Colors Used to Display Comparison Results                                                          |            |

| Signal Grouping                                                                                    |            |

| Data to Stream from Parallel Simulations                                                           |            |

| Options for Saving and Loading Session Files                                                       | 30         |

| Signal Display Units                                                                               | 30         |

|                                                                                                    |            |

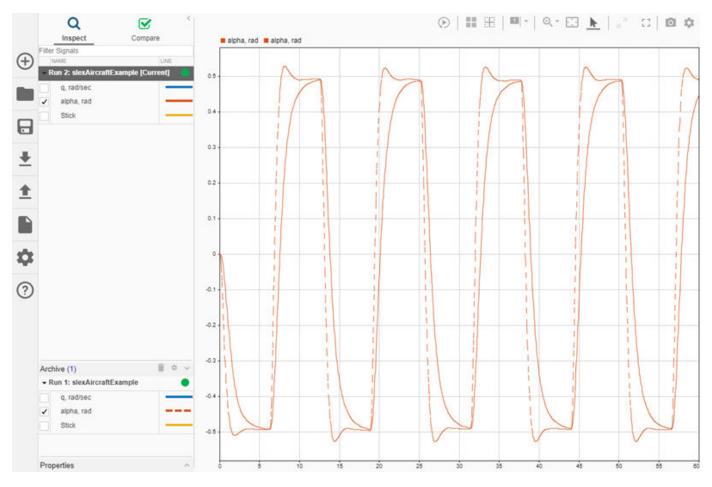

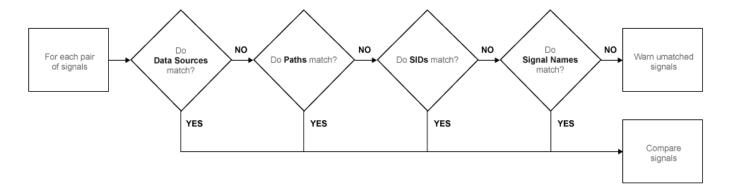

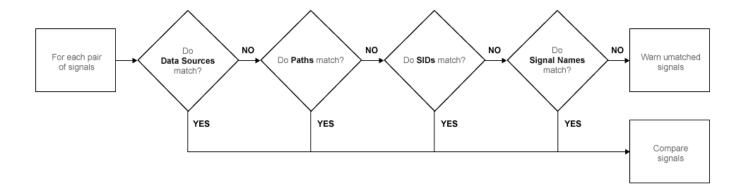

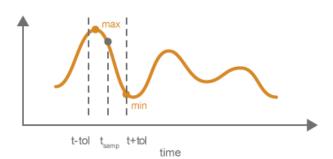

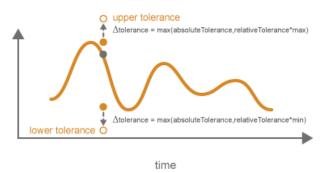

| How the Simulation Data Inspector Compares Data                                                    |            |

| Signal Alignment                                                                                   |            |

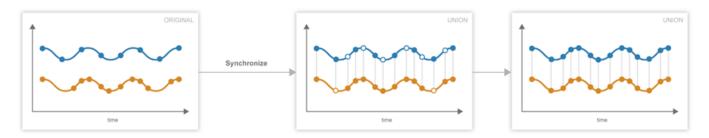

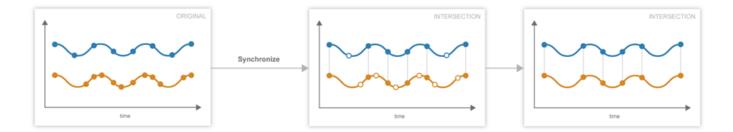

| Synchronization                                                                                    |            |

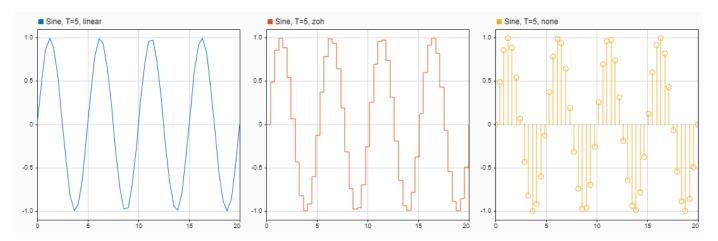

| Interpolation                                                                                      |            |

| Limitations                                                                                        |            |

|                                                                                                    | . •        |

| Save and Share Simulation Data Inspector Data and Views 5-3                                        | 37         |

| Save and Load Simulation Data Inspector Sessions                                                   |            |

| Share Simulation Data Inspector Views                                                              |            |

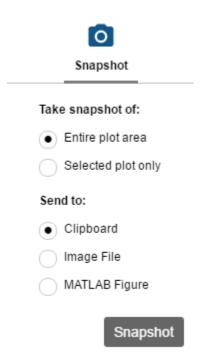

| Share Simulation Data Inspector Plots                                                              |            |

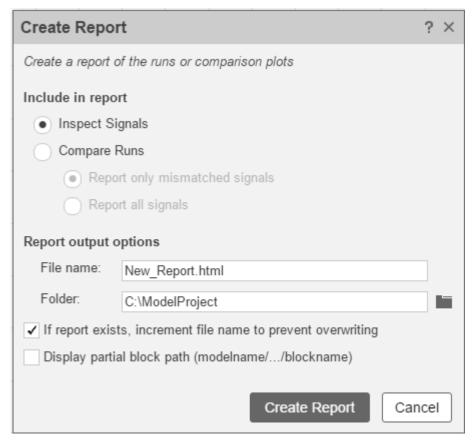

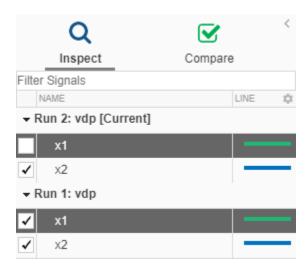

| Create a Simulation Data Inspector Report                                                          |            |

| Export Data to the Workspace or a File                                                             |            |

| Inspect and Compare Data Programmatically                           | <b>5-43</b>  |

|---------------------------------------------------------------------|--------------|

| Create a Run and View the Data                                      | <b>5-4</b> 3 |

| Compare Two Signals in the Same Run                                 | 5-44         |

| Compare Runs with Global Tolerance                                  | 5-45         |

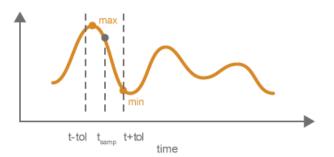

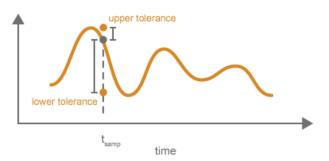

| Analyze Simulation Data Using Signal Tolerances                     | 5-46         |

| Limit the Size of Logged Data                                       | 5-48         |

| Limit the Number of Runs Retained in the Simulation Data Inspector  |              |

| Archive                                                             | <b>5-48</b>  |

| Specify a Minimum Disk Space Requirement or Maximum Size for Logged |              |

| Data                                                                | <b>5-48</b>  |

| View Data Only During Simulation                                    | 5-49         |

| Reduce the Number of Data Points Logged from Simulation             | <b>5-49</b>  |

# **Streaming Pixel Interface**

# **Streaming Pixel Interface**

#### In this section...

"What Is a Streaming Pixel Interface?" on page 1-2

"How Does a Streaming Pixel Interface Work?" on page 1-2

"Why Use a Streaming Pixel Interface?" on page 1-3

"Pixel Stream Conversion Using Blocks and System Objects" on page 1-4

"Timing Diagram of Single Pixel Serial Interface" on page 1-6

"Timing Diagram of Multipixel Serial Interface" on page 1-7

# What Is a Streaming Pixel Interface?

In hardware, processing an entire frame of video at one time has a high cost in memory and area. To save resources, serial processing is preferable in HDL designs. Vision HDL Toolbox blocks and System objects operate on a pixel, line, or neighborhood rather than a frame. The blocks and objects accept and generate video data as a serial stream of pixel data and control signals. The control signals indicate the relative location of each pixel within the image or video frame. The protocol mimics the timing of a video system, including inactive intervals between frames. Each block or object operates without full knowledge of the image format, and can tolerate imperfect timing of lines and frames.

All Vision HDL Toolbox blocks and System objects support single pixel streaming (with 1 pixel per cycle). Some blocks and System objects also support multipixel streaming (with 4 or 8 pixels per cycle) for high-rate or high-resolution video. Multipixel streaming increases hardware resources to support higher video resolutions with the same hardware clock rate as a smaller resolution video. HDL code generation for multipixel streaming is not supported with System objects. Use the equivalent blocks to generate HDL code for multipixel algorithms.

# **How Does a Streaming Pixel Interface Work?**

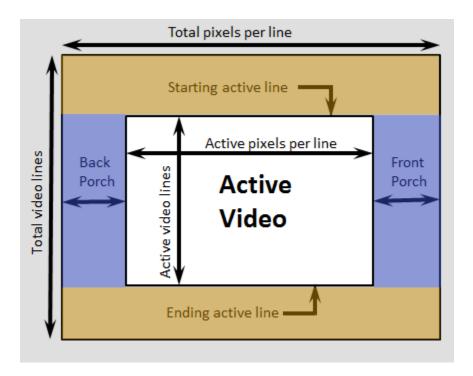

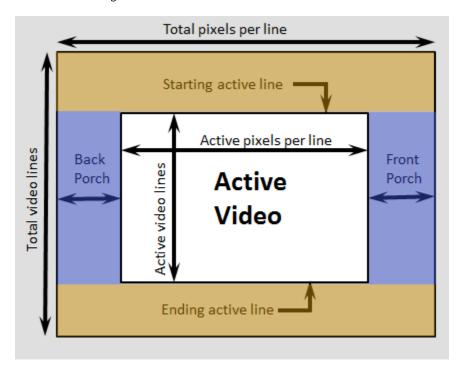

Video capture systems scan video signals from left to right and from top to bottom. As these systems scan, they generate inactive intervals between lines and frames of active video.

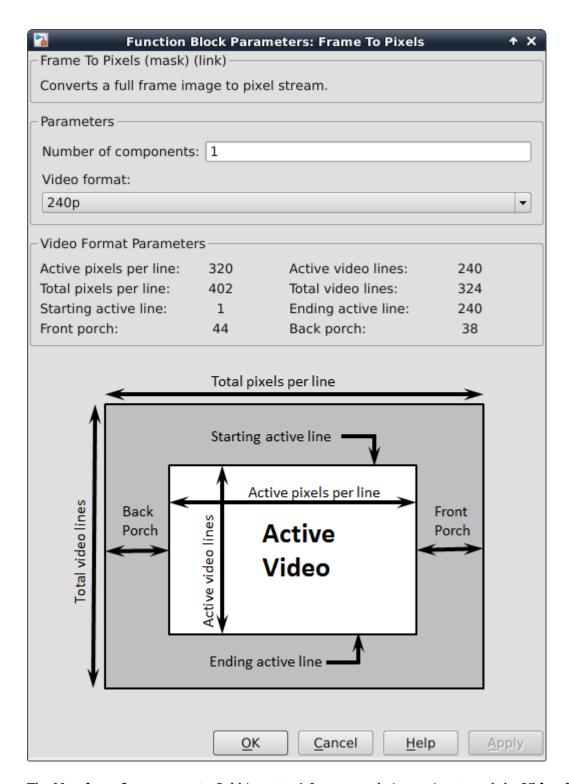

The horizontal blanking interval is made up of the inactive cycles between the end of one line and the beginning of the next line. This interval is often split into two parts: the front porch and the back porch. These terms come from the synchronize pulse between lines in analog video waveforms. The front porch is the number of samples between the end of the active line and the synchronize pulse. The back porch is the number of samples between the synchronize pulse and the start of the active line.

The *vertical blanking* interval is made up of the inactive cycles between the *ending active line* of one frame and the *starting active line* of the next frame.

The scanning pattern requires start and end signals for both horizontal and vertical directions. The Vision HDL Toolbox streaming pixel protocol includes the blanking intervals, and allows you to configure the size of the active and inactive frame.

In the frame diagram, the blue shaded area to the left and right of the active frame indicates the horizontal blanking interval. The orange shaded area above and below the active frame indicates the vertical blanking interval. For more information on blanking intervals, see "Configure Blanking Intervals" on page 2-2.

## Why Use a Streaming Pixel Interface?

#### **Format Independence**

The blocks and objects using this interface do not need a configuration option for the exact image size or the size of the inactive regions. In addition, if you change the image format for your design, you do not need to update each block or object. Instead, update the image parameters once at the serialization step. Some blocks and objects still require a line buffer size parameter to allocate memory resources.

By isolating the image format details, you can develop a design using a small image for faster simulation. Then once the design is correct, update to the actual image size.

#### **Error Tolerance**

Video can come from various sources such as cameras, tape storage, digital storage, or switching and insertion gear. These sources can introduce timing problems. Human vision cannot detect small variance in video signals, so the timing for a video system does not need to be perfect. Therefore, video processing blocks must tolerate variable timing of lines and frames.

By using a streaming pixel interface with control signals, each Vision HDL Toolbox block or object starts computation on a fresh segment of pixels at the start-of-line or start-of-frame signal. The computation occurs whether or not the block or object receives the end signal for the previous segment.

The protocol tolerates minor timing errors. If the number of valid and invalid cycles between start signals varies, the blocks or objects continue to operate correctly. Some Vision HDL Toolbox blocks and objects require minimum horizontal blanking regions to accommodate memory buffer operations. For more information, see "Configure Blanking Intervals" on page 2-2.

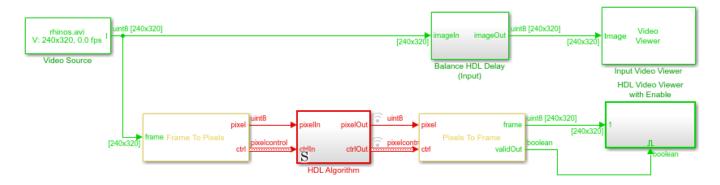

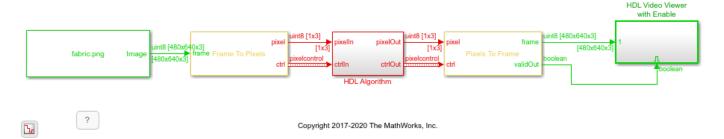

#### Pixel Stream Conversion Using Blocks and System Objects

In Simulink®, use the Frame To Pixels block to convert framed video data to a stream of pixels and control signals that conform to this protocol. The control signals are grouped in a nonvirtual bus data type called pixelcontrol. You can configure the block to return a pixel stream with 1, 4, or 8 pixels per cycle.

In MATLAB®, use the visionhdl.FrameToPixels object to convert framed video data to a stream of pixels and control signals that conform to this protocol. The control signals are grouped in a structure data type. You can configure the object to create a pixel stream with 1, 4, or 8 pixels per cycle.

If your input video is already in a serial format, you can design your own logic to generate pixelcontrol control signals from your existing serial control scheme. For example, see "Convert Camera Control Signals to pixelcontrol Format" on page 1-24 and "Integrate Vision HDL Blocks into Camera Link System" on page 1-29.

#### **Supported Pixel Data Types**

Vision HDL Toolbox blocks and objects include ports or arguments for streaming pixel data. Each block and object supports one or more pixel formats. The supported formats vary depending on the operation the block or object performs. This table details common video formats supported by Vision HDL Toolbox.

| Type of Video | Pixel Format                                                                                                                                                                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary        | Each pixel is represented by a single boolean or logical value. Used for true black-and-white video.                                                                                                                                                |

| Grayscale     | Each pixel is represented by <i>luma</i> , which is the gamma-corrected luminance value. This pixel is a single unsigned integer or fixed-point value.                                                                                              |

| Color         | Each pixel is represented by 2 to 4 unsigned integer or fixed-point values representing the color components of the pixel. Vision HDL Toolbox blocks and objects use gamma-corrected color spaces, such as R'G'B' and Y'CbCr.                       |

|               | To process multicomponent streams for blocks that do not support multicomponent input, replicate the block for each component. The pixelcontrol bus for all components is identical, so you can connect a single bus to multiple replicated blocks. |

|               | To set up multipixel streaming for color video, you can configure the Frame To Pixels block to return a multicomponent and multipixel stream. See "MultiPixel-MultiComponent Video Streaming" on page 1-18.                                         |

Vision HDL Toolbox blocks have an input or output port, pixel, for the pixel data. Vision HDL Toolbox System objects expect or return an argument representing the pixel data. The following table describes the format of the pixel data.

| Port or Argument | Description                                                                                                                                                                                                                                                                                                                                                   | Data Type                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| pixel            | <ul> <li>Single pixel streaming — A scalar that represents a binary or grayscale pixel value or a row vector of two to four values representing a color pixel</li> <li>Multipixel streaming — Column vector of four or eight pixel values</li> <li>Multipixel-multicomponent streaming — Matrix of four or eight pixel values by two to four color</li> </ul> | · · · · · · · · · · · · · · · · · · · |

|                  | generation. Use the equivalent blocks to generate HDL code for multipixel algorithms.                                                                                                                                                                                                                                                                         |                                       |

**Note** These blocks support multipixel streaming.

- Image Filter

- · Edge Detector

- · Median Filter

- ROI Selector

- · Line Buffer

- · Lookup Table

- Pixel Stream Aligner

- Pixel Stream FIFO

- · Binary morphology: Closing, Dilation, Erosion, and Opening

These blocks support multipixel-multicomponent streaming.

- Color Space Converter

- Demosaic Interpolator

- · ROI Selector

- Pixel Stream Aligner

- Pixel Stream FIFO

#### **Streaming Pixel Control Signals**

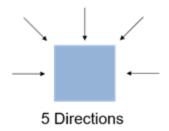

Vision HDL Toolbox blocks and objects include ports or arguments for control signals relating to each pixel. These five control signals indicate the validity of a pixel and its location in the frame. For multipixel streaming, each vector of pixel values has one set of control signals.

In Simulink, the control signal port is a nonvirtual bus data type called pixelcontrol. For details of the bus data type, see "Pixel Control Bus" on page 1-22.

In MATLAB, the control signal argument is a structure. For details of the structure data type, see "Pixel Control Structure" on page 1-23.

#### **Timing Diagram of Single Pixel Serial Interface**

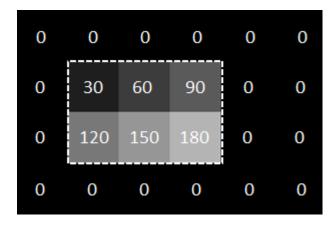

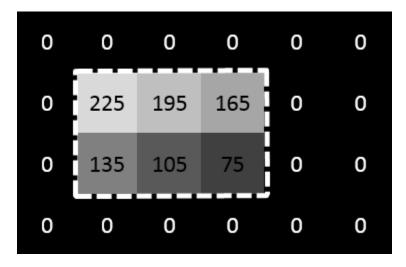

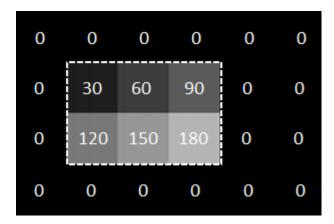

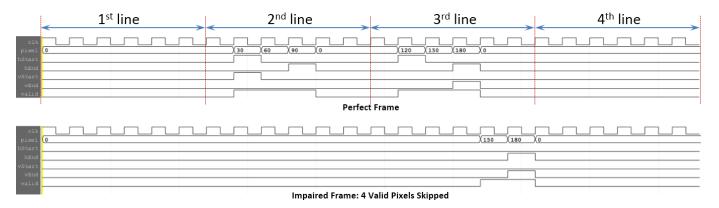

To illustrate the streaming pixel protocol, this example converts a frame to a sequence of control and data signals. Consider a 2-by-3 pixel image. To model the blanking intervals, configure the serialized image to include inactive pixels in these areas around the active image:

- 1-pixel-wide back porch

- 2-pixel-wide front porch

- 1 line before the first active line

- 1 line after the last active line

You can configure the dimensions of the active and inactive regions with the Frame To Pixels block or the visionhdl.FrameToPixels object.

In the figure, the active image area is in the dashed rectangle, and the inactive pixels surround it. The pixels are labeled with their grayscale values.

The block or object serializes the image from left to right, one line at a time. The timing diagram shows the control signals and pixel data that correspond to this image, which is the serial output of the Frame To Pixels block for this frame, configured for single-pixel streaming.

For an example using the Frame to Pixels block to serialize an image, see "Design Video Processing Algorithms for HDL in Simulink".

For an example using the FrameToPixels object to serialize an image, see "Design a Hardware-Targeted Image Filter in MATLAB".

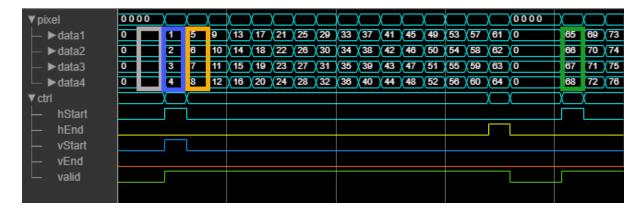

#### Timing Diagram of Multipixel Serial Interface

This example converts a frame to a multipixel stream with 4 pixels per cycle and corresponding control signals. Consider a 64-pixel-wide frame with these inactive areas around the active image.

- 4-pixel-wide back porch

- 4-pixel-wide front porch

- 4 lines before the first active line

- 4 lines after the last active line

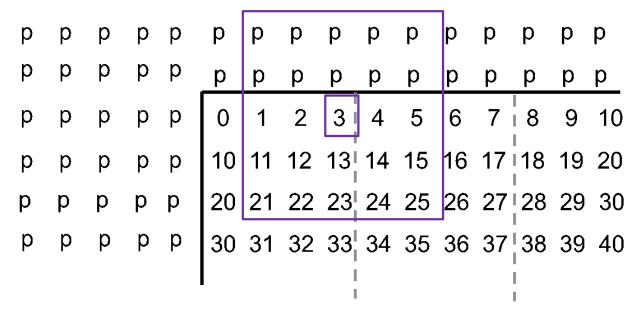

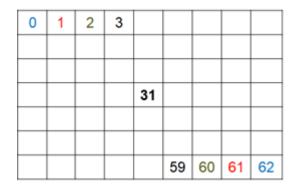

The Frame to Pixels block configured for multipixel streaming returns pixel vectors formed from the pixels of each line in the frame from left to right. This diagram shows the top-left corner of the frame. The gray pixels show the active area of the frame, and the zero-value pixels represent blanking pixels. The label on each active pixel represents the location of the pixel in the frame. The highlighted boxes show the sets of pixels streamed on one cycle. The pixels in the inactive region are also streamed four at a time. The gray box shows the four blanking pixels streamed the cycle before the start of the active frame. The blue box shows the four pixel values streamed on the first valid cycle of the frame, and the orange box shows the four pixel values streamed on the second valid cycle of the frame. The green box shows the first four pixels of the next active line.

| 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|---|---|---|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0 | 0 | 0 | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  |

| 0 | 0 | 0 | 0 | 65  | 66  | 67  | 68  | 69  | 70  | 71  | 72  | 73  | 74  |

| 0 | 0 | 0 | 0 | 129 | 130 | 131 | 132 | 133 | 134 | 135 | 136 | 137 | 138 |

| 0 | 0 | 0 | 0 | 193 | 194 | 195 | 196 | 197 | 198 | 199 | 200 | 201 | 202 |

| 0 | 0 | 0 | 0 | 257 | 258 | 259 | 260 | 261 | 262 | 263 | 264 | 265 | 266 |

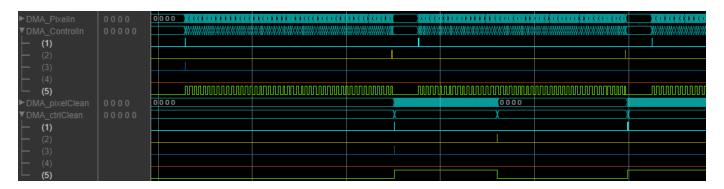

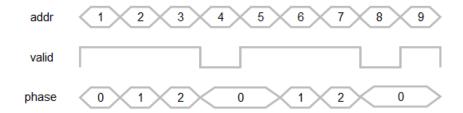

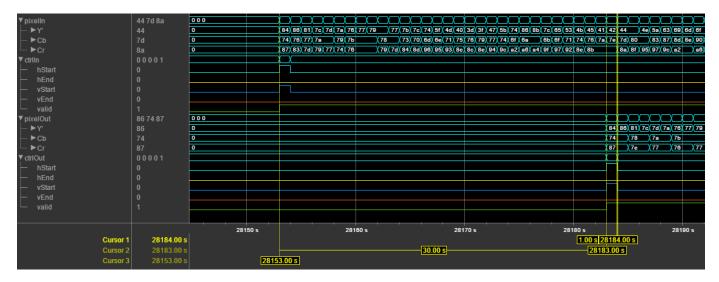

This waveform shows the multipixel streaming data and control signals for the first line of the same frame, streamed with 4 pixels per cycle. The pixelcontrol signals that apply to each set of four pixel values are shown below the data signals. Because the vector has only one valid signal, the pixels in the vector are either all valid or all invalid. The hStart and vStart signals apply to the pixel with the lowest index in the vector. The hEnd and vEnd signals apply to the pixel with the highest index in the vector.

Prior to the time period shown, the initial vertical blanking pixels are streamed four at a time, with all control signals set to false. This waveform shows the pixel stream of the first line of the image. The gray, blue, and orange boxes correspond to the highlighted areas of the frame diagram. After the first line is complete, the stream has two cycles of horizontal blanking that contains 8 invalid pixels (front and back porch). Then, the waveform shows the next line in the stream, starting with the green box.

For an example model that uses multipixel streaming, see "Filter Multipixel Video Streams" on page 1-9.

#### See Also

Frame To Pixels | Pixels To Frame | visionhdl.FrameToPixels | visionhdl.PixelsToFrame

## **Related Examples**

- "Design Video Processing Algorithms for HDL in Simulink"

- "Design a Hardware-Targeted Image Filter in MATLAB"

- "Filter Multipixel Video Streams" on page 1-9

- "MultiPixel-MultiComponent Video Streaming" on page 1-18

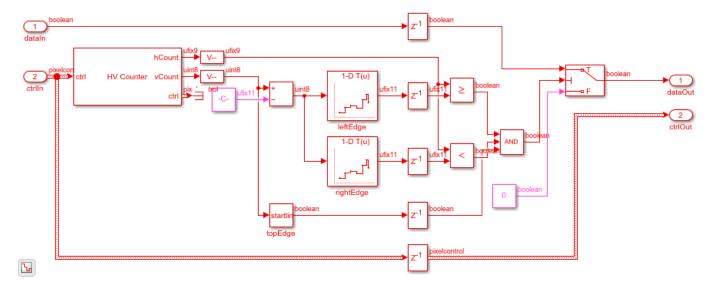

# **Filter Multipixel Video Streams**

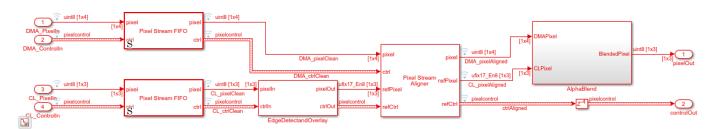

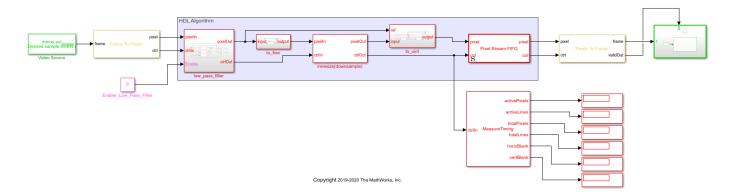

This example shows how to design filters that operate on a multipixel input video stream. Use multipixel streaming to process high-resolution or high-frame-rate video with the same synthesized clock frequency as a single-pixel streaming interface. Multipixel streaming also improves simulation speed and throughput because fewer iterations are required to process each frame, while maintaining the hardware benefits of a streaming interface.

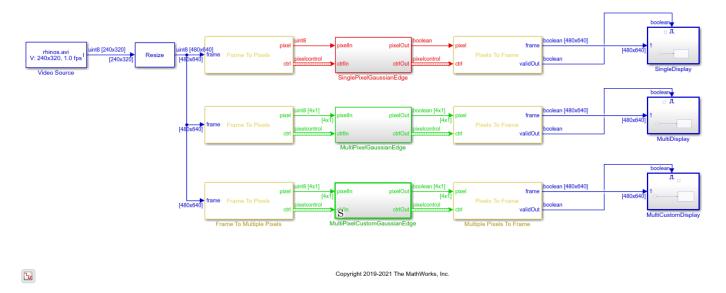

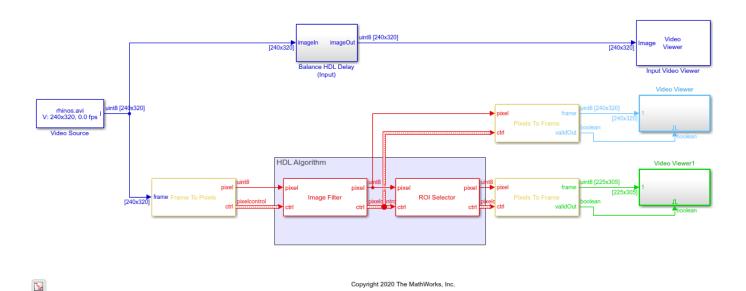

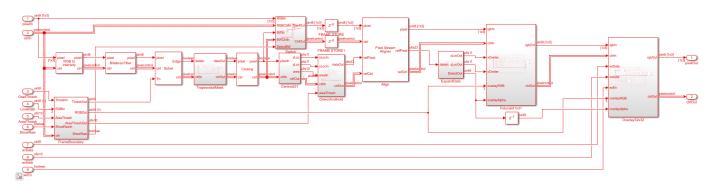

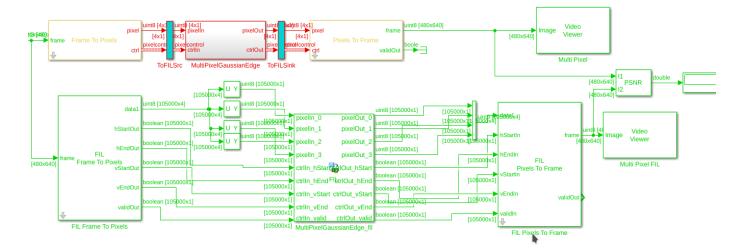

The example model has three subsystems which each perform the same algorithm:

- SinglePixelGaussianEdge: Uses the Image Filter and Edge Detector blocks to operate on a single-pixel stream. This subsystem shows how the rates and interfaces for single-pixel streaming compare with multipixel designs.

- **MultiPixelGaussianEdge**: Uses the Image Filter and Edge Detector blocks to operate on a multipixel stream. This subsystem shows how to use the multipixel interface with library blocks.

- **MultiPixelCustomGaussianEdge**: Uses the Line Buffer block to build a Gaussian filter and Sobel edge detection for a multipixel stream. This subsystem shows how to use the Line Buffer output for multipixel design.

Processing multipixel video streams allows for higher frame rates to be achieved without a corresponding increase to the clock frequency. Each of the subsystems can achieve 200MHz clock frequency on a Xilinx ZC706 board. The 480p video stream has **Total pixels per line** x **Total video lines** = 800\*525 cycles per frame. With a single pixel stream you can process 200M/(800\*525) = 475 frames per second. In the multipixel subsystem, 4 pixels are processed on each cycle, which reduces the number of cycles per line to 200. This means that with a multipixel stream operating on 4 pixels at a time, at 200MHz, on a 480p stream, 1900 frames can be processed per second. If the resolution is increased from 480p to 1080p, 80 frames per second can be achieved in the single pixel case versus 323 frames per second for 4 pixels at a time or 646 frames per second for 8 pixels at a time.

#### **Multipixel Streaming Using Library Blocks**

Generate a multipixel stream from the Frame to Pixels block by setting **Number of pixels** to 4 or 8. The default value of 1 returns a scalar pixel stream with a sample rate of **Total pixels per line** \*

**Total video lines** faster than the frame rate. This rate shows red in the example model. The two multipixel subsystems use a multipixel stream with **Number of pixels** set to 4. This configuration returns 4 pixels on each clock cycle and has a sample rate of (**Total pixels per line**/4) \* **Total video lines**. The lower output rate, which is green in the model, shows that you can increase either the input frame rate or resolution by a factor of 4 and therefore process 4 times as many pixels in the same frame period using the same clock frequency as the single pixel case.

The **SinglePixelGaussianEdge** and **MultiPixelGaussianEdge** subsystems compute the same result using the Image Filter and Edge Detector blocks.

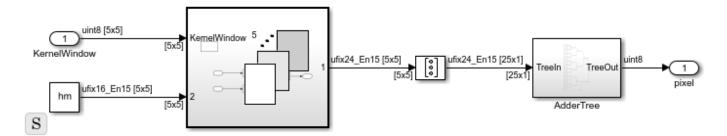

In **MultiPixelGaussianEdge**, the blocks accept and return four pixels on each clock cycle. You do not have to configure the blocks for multipixel streaming, they detect the input size on the port. The pixelcontrol bus indicates the validity and location in the frame of each set of four pixels. The blocks buffer the [4x1] stream to form four [KernelHeight x KernelWidth] kernels, and compute four convolutions in parallel to give a [4x1] output.

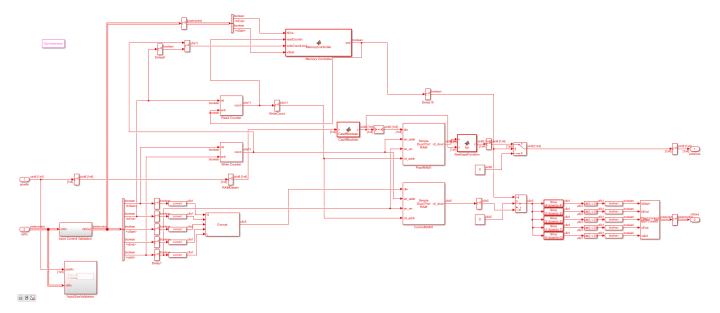

#### **Custom Multipixel Algorithms**

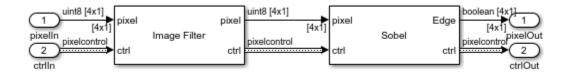

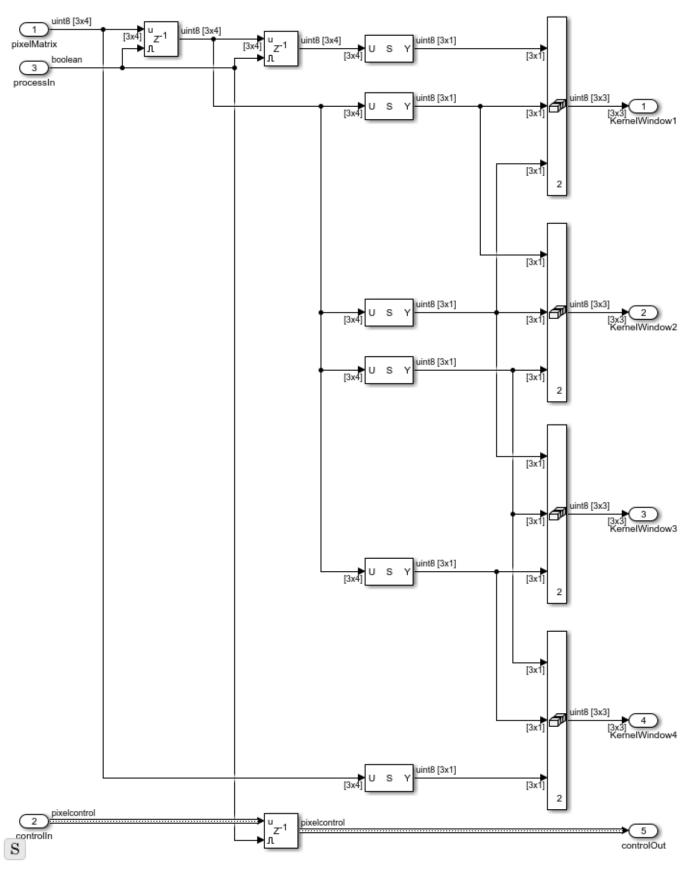

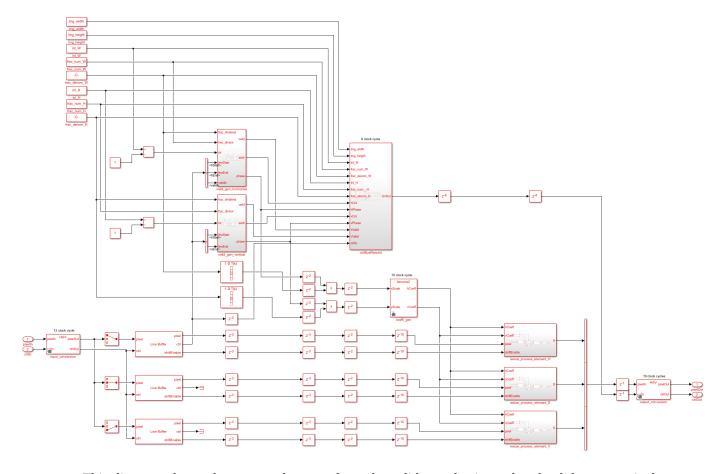

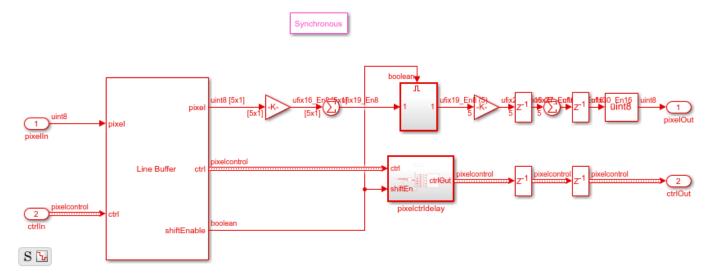

The **MultiPixelCustomGaussianEdge** subsystem uses the Line Buffer block to implement a custom filtering algorithm. This subsystem is similar to how the library blocks internally implement multipixel kernel operations. The Image Filter and Edge Detector blocks use more detailed optimizations than are shown here. This implementation shows a starting point for building custom multipixel algorithms using the output of the Line Buffer block.

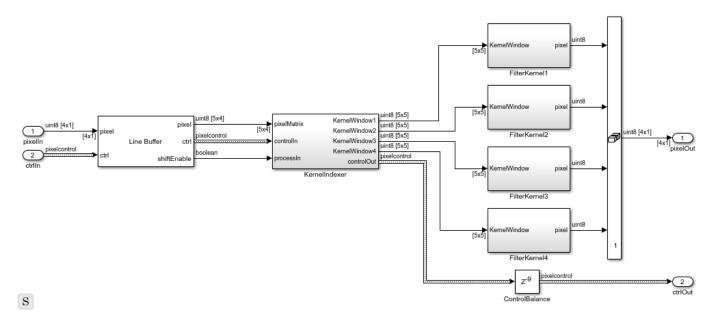

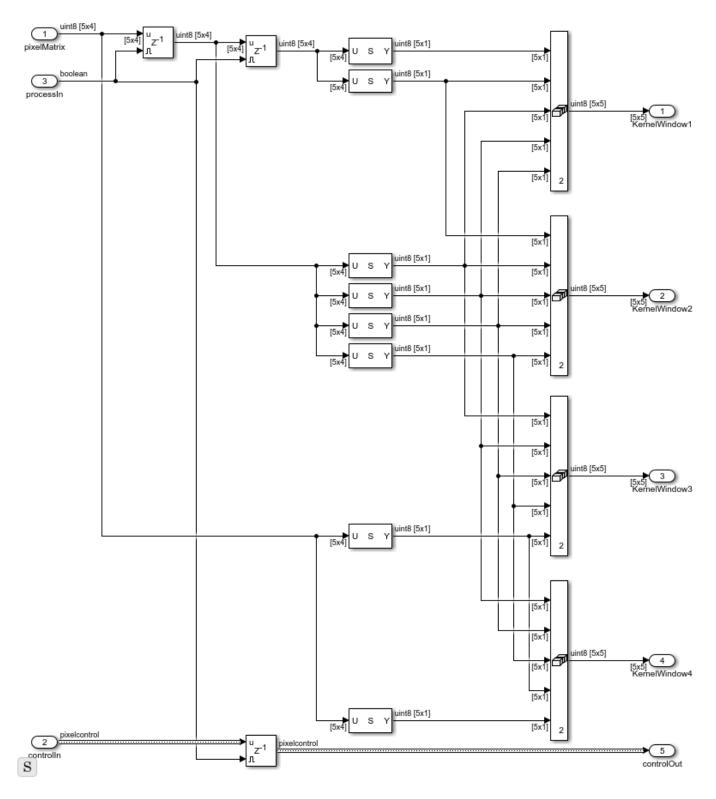

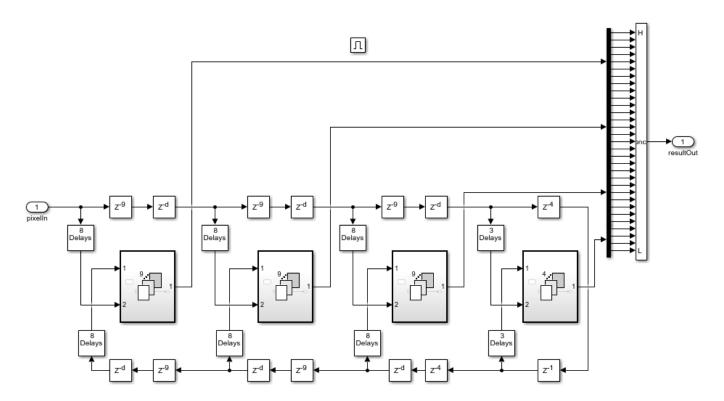

The custom filter and custom edge detector use the Line Buffer block to return successive [ KernelHeight x NumberofPixels ] regions. Each region is passed to the KernelIndexer subsystem which uses buffering and indexing logic to form Number of Pixels \* [ KernelHeight x KernelWidth ] filter kernels. Then each kernel is passed to a separate FilterKernel subsystem to perform convolutions in parallel.

## Form Kernels from Line Buffer Output

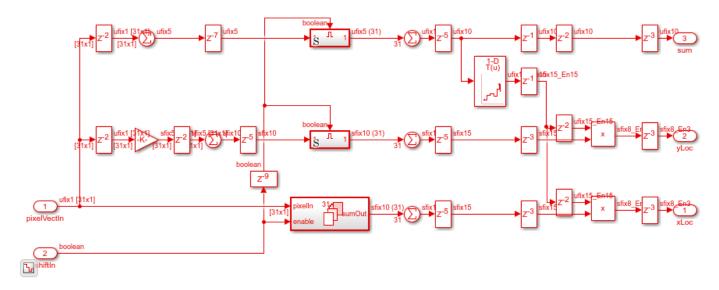

The KernelIndexer subsystem forms  $4\ [5x5]$  filter kernels from the 2-D output of the Line Buffer block.

The diagram shows how the filter kernel is extracted from the [5x4] output stream, for the kernel that is centered on the first pixel in the [4x1] output. This first kernel includes pixels from 2 adjacent [5x4] Line Buffer outputs.

| р | p | р | р | р | р  | р  | р  | p               | p  | p  | p  | p  | р    | p  | p  |

|---|---|---|---|---|----|----|----|-----------------|----|----|----|----|------|----|----|

| р | p | р | р | р | р  | р  | р  | р               | р  | р  | р  | р  | р    | р  | р  |

| р | р | р | р | р | 0  | 1  | 2  | 3               | 4  | 5  | 6  | 7  | 8    | 9  | 10 |

| р | р | р | р | р | 10 | 11 | 12 | 13              | 14 | 15 | 16 | 17 | 18   | 19 | 20 |

| p | p | р | р | р | 20 | 21 | 22 | 23 <sup>1</sup> | 24 | 25 | 26 | 27 | 28   | 29 | 30 |

| р | р | р | р | p | 30 | 31 | 32 | 33 <sup>1</sup> | 34 | 35 | 36 | 37 | 38   | 39 | 40 |

|   |   |   |   |   | l  |    |    |                 |    |    |    |    | <br> |    |    |

The kernel centered on the last pixel in the [4x1] output also includes the third adjacent [5x4] output. So, to form four [5x5] kernels, the subsystem must access columns from three [5x4] matrices.

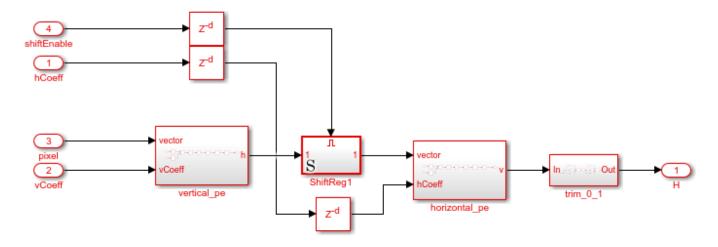

The KernelIndexer subsystem uses the current [5x4] input, and stores two more [5x4] matrices using registers enabled by shiftEnable. This design is similar to the tapped delay line used with a Line Buffer using single pixel streaming. The subsystem then accesses pixel data across the columns to form the four [5x5] kernels. The Image Filter block uses this same logic internally when the block has multipixel input. The block automatically designs this logic at compile time for any supported kernel size.

#### **Implement Filters**

Since the input multipixel stream is a [4x1] vector, the filters must perform four convolutions on each cycle to keep pace with the incoming data. There are four parallel FilterKernel subsystems that each

perform the same operation. The [5x5] matrix multiply is implemented as a [5x1] vector multiply by using a For Each subsystem containing a pipelined multiplier. The output is passed to an adder tree. The adder tree is also pipelined, and the pipeline latency is applied to the pixelcontrol signal to match. The results of the four FilterKernel subsystems are then concatenated into a [4x1] output vector.

#### **Implement Edge Detectors**

To match the algorithm of the Edge Detector block, this custom edge detector uses a [3x3] kernel size. Compare this KernelIndexer subsystem for the [3x3] edge detection with the [5x5] kernel described above. The algorithm still must access three successive matrices from the output of the Line Buffer block (including padding on either side of the kernel). However, the algorithm saves fewer columns to form a smaller filter kernel.

#### **Extending to Larger Kernel Sizes**

For a [4x1] multipixel stream, the KernelIndexer logic will look similar up to [11x11] kernel size. At that size, the number of padding pixels, (floor(11/2)) = 5, will overlap on two [11x4] matrices returned from the Line Buffer. This overlap means the algorithm would need to store five [5x4] matrices from the Line Buffer to form four [11x11] kernels on each cycle.

|     |   |   |   |   |        |    |    |    |    |    | _  |    |        | _  |    |

|-----|---|---|---|---|--------|----|----|----|----|----|----|----|--------|----|----|

| p l | р | р | р | р | ¦ p    | р  | р  | р  | p  | р  | р  | р  | p p    | р  | р  |

| p ¦ | р | p | р | p | ¦p     | p  | p  | p  | р  | p  | р  | p  | p      | р  | p  |

| р¦  | р | p | p | p | þ      | p  | p  | p  | р  | p  | р  | p  | p      | р  | p  |

| р   | р | p | р | p | p      | р  | р  | p  | p  | p  | р  | p  | р      | р  | p  |

| p   | р | p | р | p | p      | p  | р  | p  | p  | р  | р  | р  | p      | р  | р  |

| р¦  | р | p | р | p | 0      | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8      | 9  | 10 |

| р   | р | p | р | p | 10     | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18     | 19 | 20 |

| p ¦ | р | p | р | p | 20     | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28     | 29 | 30 |

| p ¦ | р | p | р | p | 30     | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38     | 39 | 40 |

| p¦  | р | p | p | p | 40     | 41 | 42 | 43 | 43 | 45 | 46 | 47 | 48     | 49 | 50 |

| p l | р | р | р | р | ¦ 50   | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58     | 59 | 60 |

| I   |   |   |   |   | I<br>I |    |    |    |    |    |    |    | l<br>I |    |    |

|     |   |   |   |   | <br>   |    |    |    |    |    |    |    | <br>   |    |    |

|     |   |   |   |   | <br>   |    |    |    |    |    |    |    | <br>   |    |    |

#### **Improving Simulation Time**

In the default example configuration, the single pixel, multipixel, and custom multipixel subsystems all run in parallel. The simulation speed is limited by the time processing the single-pixel path because it requires more iterations to process the same size of frame. To observe the simulation speed improvement for multipixel streaming, comment out the single-pixel data path.

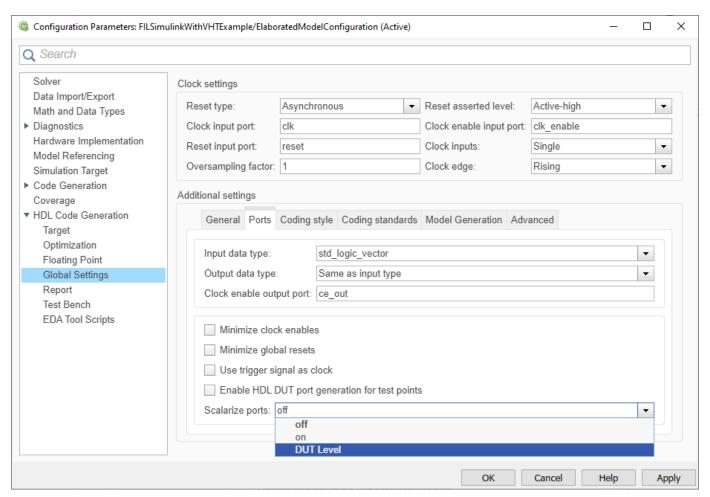

#### **HDL Implementation Results**

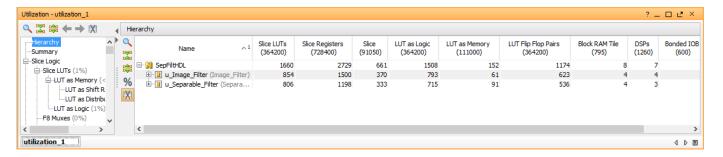

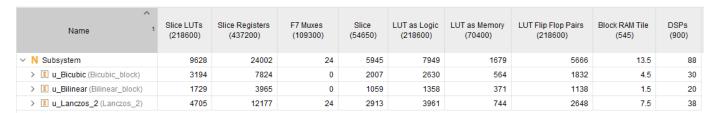

HDL was generated from both the **MultiPixelGaussianEdge** subsystem and the **MultiPixelCustomGaussianEdge** subsystem and put through Place and Route on a Xilinx $^{\text{m}}$  ZC706 board. The **MultiPixelCustomGaussianEdge** subsystem, which does not attempt to optimize coefficients, had the following results -

T =

4x2 table

Resource Usage

DSP48 108

Flip Flop 9842

LUT 4960

BRAM 12

The **MultiPixelGaussianEdge** subsystem, which uses the optimized Image Filter and Edge Detector blocks uses less resources, as shown in the table below. This comparison shows the resource savings achieved because the blocks analyze the filter structure and pre-add repeated coefficients.

T =

4x2 table

Resource Usage

DSP48 16

Flip Flop 3959

LUT 1789

BRAM 10

#### See Also

Frame To Pixels | Image Filter | Edge Detector | Pixels To Frame

#### **More About**

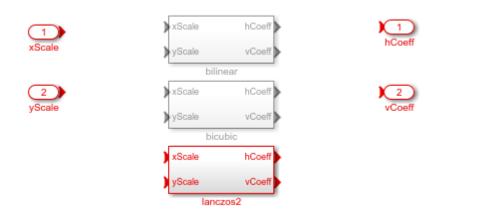

# MultiPixel-MultiComponent Video Streaming

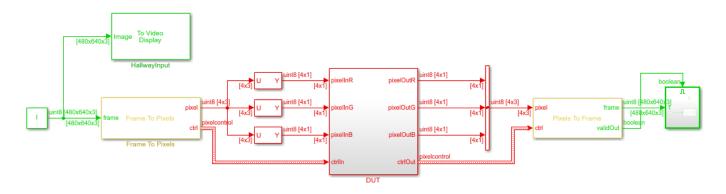

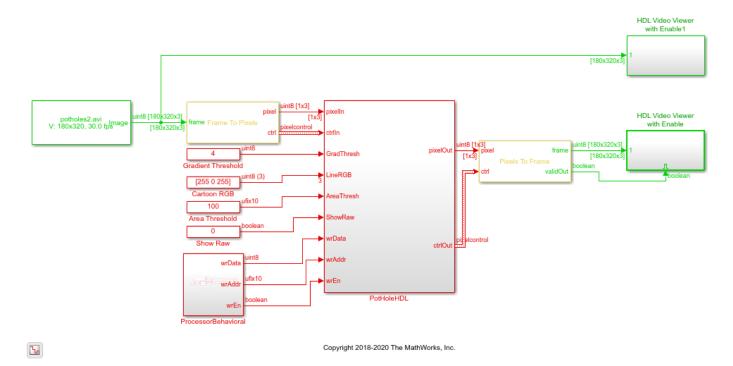

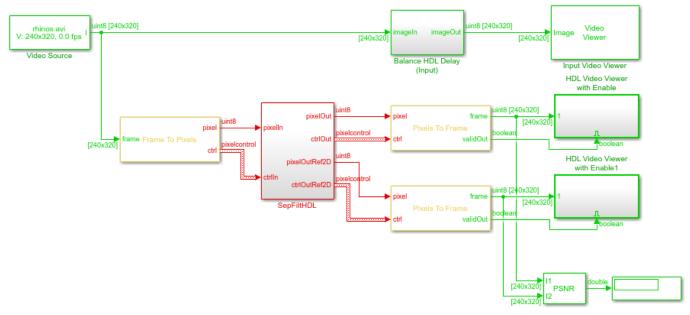

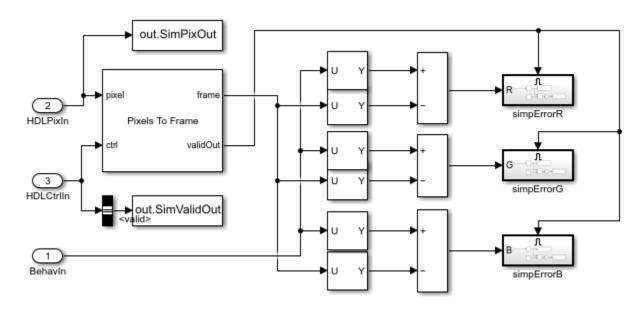

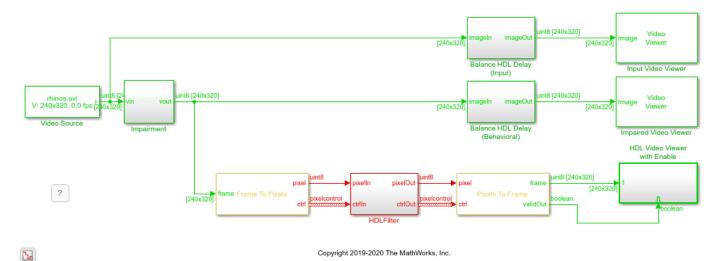

This example shows how to work with a multipixel-multicomponent pixel stream. Multipixel-multicomponent streaming enables real-time processing of high-resolution or high-frame-rate color video streams.

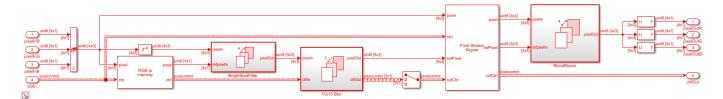

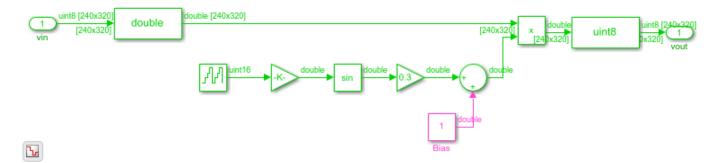

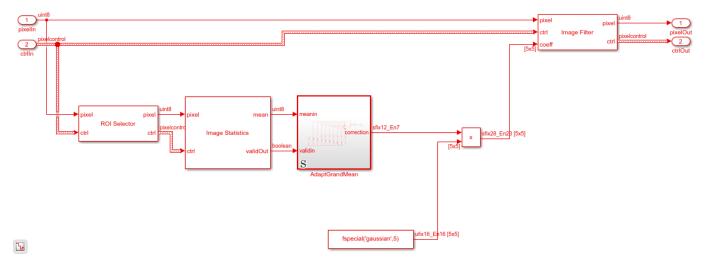

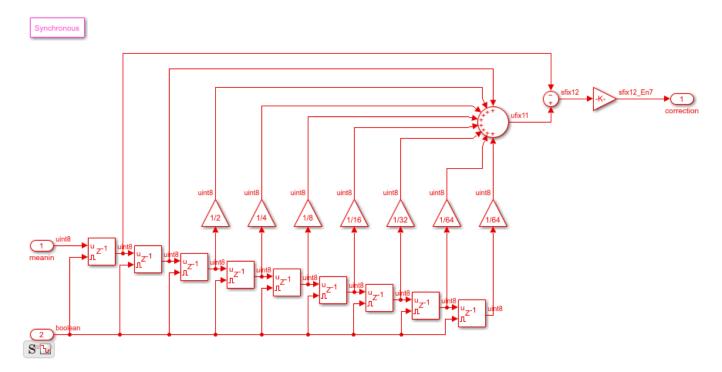

To demonstrate working with such a video stream, this example implements the well-known *bloom effect* image post-processing technique. The bloom effect introduces or enhances the glow of light sources in an image.

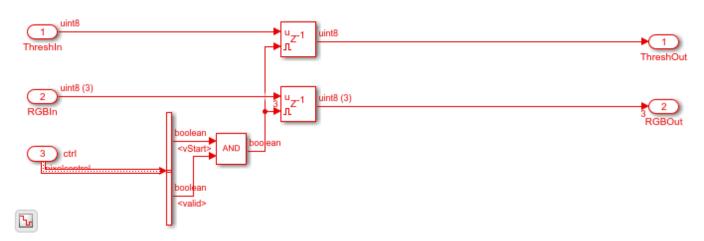

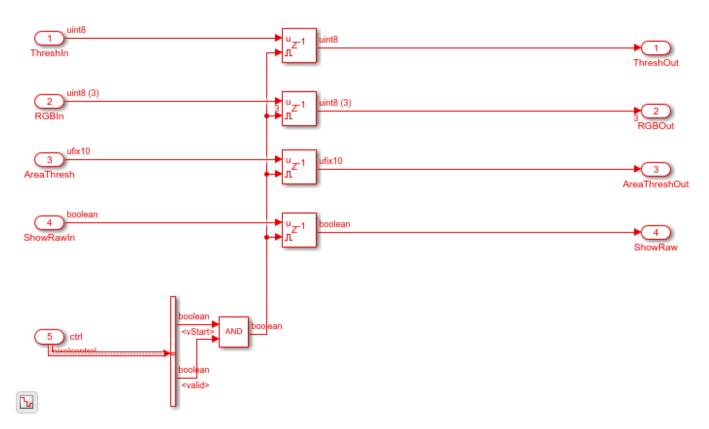

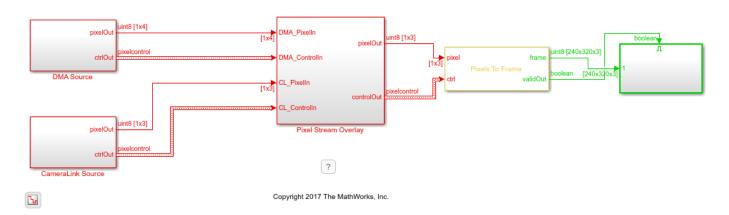

#### Top Level I/0

Each pixel of a high-resolution or high-frame-rate pixel stream is modeled as a NumPixel-by-NumComponent matrix. Matrix data types are supported for HDL code generation within a design, but not for the ports of the top-level subsystem. In this case, the input pixel stream is split into three 4-by-1 vectors at the input of the DUT, and then recombined at the output into a 4-by-3 matrix for the Pixels To Frame block.

Copyright 2019-2021 The MathWorks, Inc

#### **Bloom Effect**

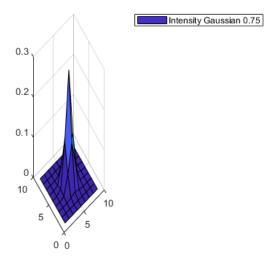

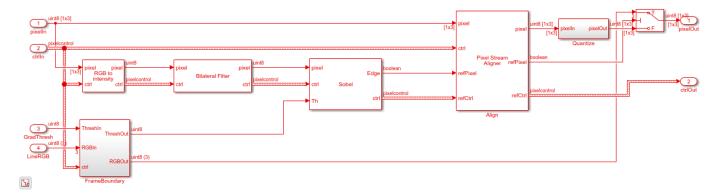

The example model follows these three steps to add a bloom effect to the input image.

- The BrightSpotFilter subsystems find bright spots in the intensity image by checking pixel values against a threshold. These pixel values have been converted from RGB to intensity by the Color Space Converter.

- 2 The 15x15 Blur subsystem spreads out the bright spots by applying a Gaussian filter.

- **3** The BlendBloom subsystem adds the Gaussian-enhanced bright spots back to the original image.

#### **Matrix Operations**

Vision HDL Toolbox™ neighborhood-processing blocks can operate on vector inputs, but do not support matrix inputs. The line buffer used inside the blocks returns a NumPixels-by-KernelHeight matrix. Using multicomponent inputs would result in a NumPixels-by-KernelHeight-by-NumComponents output matrix, however, 3-D matrices are not supported for HDL code generation. To work around this the model uses For Each subsystems which support HDL code generation with scalar, vector, and matrix inputs.

The model sets the **Partition Width** and **Partition Dimension** of the BrightSpotFilter to 1. The subsystem applies a threshold in parallel to each 1x3 RGB multi-component pixel of its input multipixel-multicomponent matrix.

The 15x15 Blur subsystem has the **Partition Width** set to 1 and **Partition Dimension** set to 2. The subsystem applies a Gaussian filter in parallel to each 4x1 multipixel RGB component.

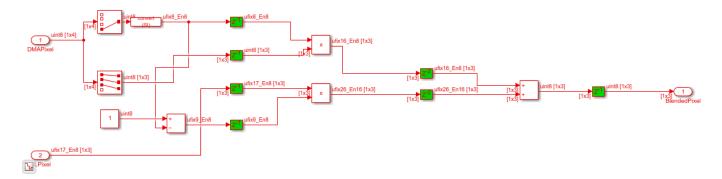

The BlendBloom subsystem has the **Partition Width** and **Partition Dimension** set to 1. The subsystem adds in parallel each 1x3 multicomponent pixel to its respective filtered 1x3 multicomponent pixel.

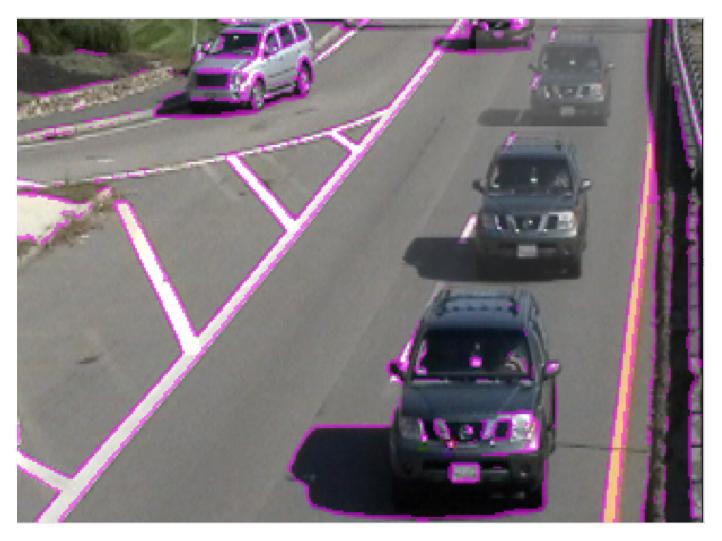

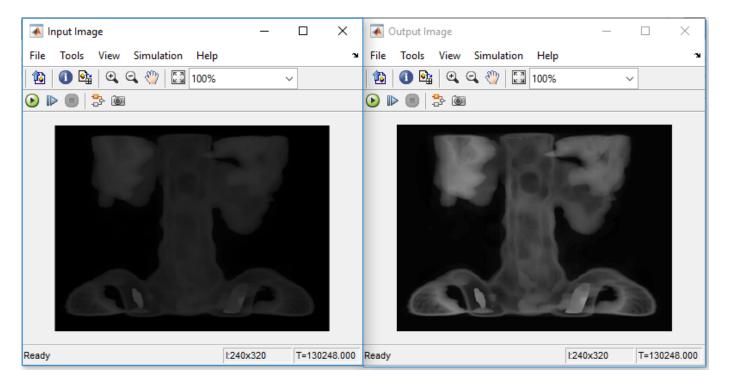

#### **Simulation Results**

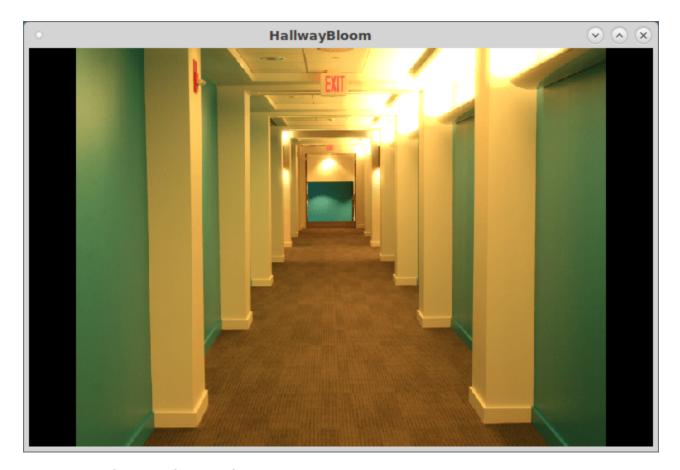

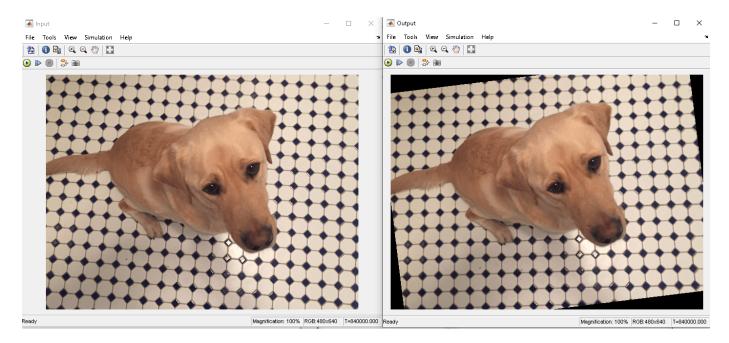

Simulating the model displays these input and output images. The bloom effect makes the lighted areas of the scene look brighter and shows a halo effect.

#### **Implementation Results**

This table shows the synthesis results of HDL code generated from the DUT subsystem and synthesized for a  $Xilinx^{TM}$   $Zynq^{TM}$  ZC706 board. Because none of the resources exceed 25% of their respective category, the design has a relatively small footprint.

T =

4x2 table

Resource Usage

DSP48 84

Flip Flop 61739

LUT 36966

BRAM 132

# See Also

Frame To Pixels | Pixels To Frame

# **More About**

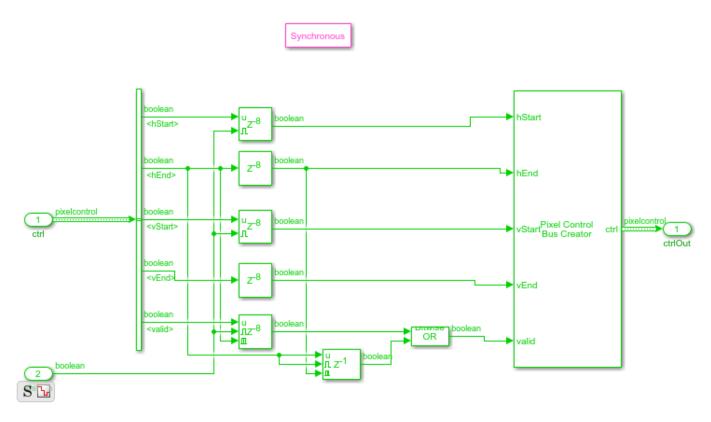

## **Pixel Control Bus**

Vision HDL Toolbox blocks use a nonvirtual bus data type, pixelcontrol, for control signals associated with serial pixel data. The bus contains 5 boolean signals indicating the validity of a pixel and its location within a frame. You can easily connect the data and control output of one block to the input of another, because Vision HDL Toolbox blocks use this bus for input and output. To convert an image into a pixel stream and a pixelcontrol bus, use the Frame to Pixels block.

| Signal | Description                                                  | Data Type |

|--------|--------------------------------------------------------------|-----------|

| hStart | true for the first pixel in a horizontal line of a frame     | boolean   |

| hEnd   | true for the last pixel in a horizontal line of a frame      | boolean   |

| vStart | true for the first pixel in the first (top) line of a frame  | boolean   |

| vEnd   | true for the last pixel in the last (bottom) line of a frame | boolean   |

| valid  | true for any valid pixel                                     | boolean   |

For multipixel streaming, each vector of pixel values has one set of control signals. Because the vector has only one valid signal, the pixels in the vector must be either all valid or all invalid. The hStart and vStart signals apply to the pixel with the lowest index in the vector. The hEnd and vEnd signals apply to the pixel with the highest index in the vector.

**Troubleshooting:** When you generate HDL code from a Simulink model that uses this bus, you may need to declare an instance of pixelcontrol bus in the base workspace. If you encounter the error Cannot resolve variable 'pixelcontrol' when you generate HDL code in Simulink, use the pixelcontrolbus function to create an instance of the bus type. Then try generating HDL code again.

To avoid this issue, the Vision HDL Toolbox model template includes this line in the InitFcn callback.

evalin('base','pixelcontrolbus')

#### See Also

Frame To Pixels | Pixels To Frame | pixelcontrolbus

#### **More About**

# **Pixel Control Structure**

Vision HDL Toolbox System objects use a structure data type for control signals associated with serial pixel data. The structure contains five logical signals indicating the validity of a pixel and its location within a frame. You can easily pass the data and control output arguments of one Vision HDL Toolbox System object. To as the input arguments to another Vision HDL Toolbox System object, because the objects use this structure for input and output control signal arguments. To convert an image into a pixel stream and control signals, use the visionhdl.FrameToPixels System object.

| Signal | Description                                                  | Data Type |

|--------|--------------------------------------------------------------|-----------|

| hStart | true for the first pixel in a horizontal line of a frame     | logical   |

| hEnd   | true for the last pixel in a horizontal line of a frame      | logical   |

| vStart | true for the first pixel in the first (top) line of a frame  | logical   |

| vEnd   | true for the last pixel in the last (bottom) line of a frame | logical   |

| valid  | true for any valid pixel                                     | logical   |

#### See Also

pixelcontrolstruct|pixelcontrolsignals|visionhdl.FrameToPixels|

visionhdl.PixelsToFrame

#### **More About**

# **Convert Camera Control Signals to pixelcontrol Format**

This example shows how to convert Camera Link® signals to the pixelcontrol structure, invert the pixels with a Vision HDL Toolbox $^{\text{\tiny M}}$  object, and convert the control signals back to the Camera Link format.

Vision HDL Toolbox blocks and objects use a custom streaming video format. If your system operates on streaming video data from a camera, you must convert the camera control signals into this custom format. Alternatively, if you integrate Vision HDL Toolbox algorithms into existing design and verification code that operates in the camera format, you must also convert the output signals from the Vision HDL Toolbox design back to the camera format.

You can generate HDL code from the three functions in this example. To create local copies of all the files in this example, so you can view and edit them, click the Open Script button.

#### **Create Input Data in Camera Link Format**

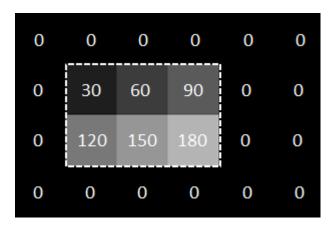

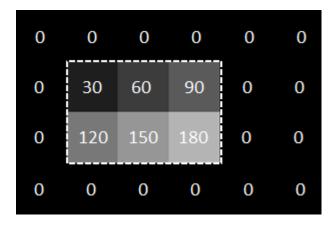

The Camera Link format consists of three control signals: F indicates the valid frame, L indicates each valid line, and D indicates each valid pixel. For this example, create input vectors in the Camera Link format to represent a basic padded video frame. The vectors describe this 2-by-3, 8-bit grayscale frame. In the figure, the active image area is in the dashed rectangle, and the inactive pixels surround it. The pixels are labeled with their grayscale values.

#### **Design Vision HDL Toolbox Algorithm**

Create a function to invert the image using Vision HDL Toolbox algorithms. The function contains a System object that supports HDL code generation. This function expects and returns a pixel and associated control signals in Vision HDL Toolbox format.

```

function [pixOut,ctrlOut] = InvertImage(pixIn,ctrlIn)

persistent invertI;

if isempty(invertI)

tabledata = linspace(255,0,256);

invertI = visionhdl.LookupTable(uint8(tabledata));

```

#### end

```

% *Note:* This syntax runs only in R2016b or later. If you are using an

% earlier release, replace each call of an object with the equivalent |step|

% syntax. For example, replace |my0bject(x)| with |step(my0bject,x)|.

[pix0ut,ctrl0ut] = invertI(pixIn,ctrlIn);

end

```

#### Convert Camera Link Control Signals to pixelcontrol Format

Write a custom System object to convert Camera Link signals to the Vision HDL Toolbox control signal format. The object converts the control signals, and then calls the pixelcontrolstruct function to create the structure expected by the Vision HDL Toolbox System objects. This code snippet shows the logic to convert the signals.

The object stores the input and output control signal values in registers. vStart goes high for one cycle at the start of F. vEnd goes high for one cycle at the end of F. hStart and hEnd are derived similarly from L. The object returns the current value of ctrl each time you call it.

This processing adds two cycles of delay to the control signals. The object passes through the pixel value after matching delay cycles. For the complete code for the System object, see CAMERALINKtoVHT Adapter.m.

#### Convert pixelcontrol to Camera Link

Write a custom System object to convert Vision HDL Toolbox signals back to the Camera Link format. The object calls the pixelcontrolsignals function to flatten the control structure into its component signals. Then it computes the equivalent Camera Link signals. This code snippet shows the logic to convert the signals.

```

[hStart,hEnd,vStart,vEnd,valid] = pixelcontrolsignals(ctrl);

Fnew = (~obj.FOutReg && vStart) || (obj.FPrevReg && ~obj.vEndReg);

Lnew = (~obj.LOutReg && hStart) || (obj.LPrevReg && ~obj.hEndReg);

obj.FOutReg = Fnew;

obj.LOutReg = Lnew;

obj.DOutReg = valid;

```

The object stores the input and output control signal values in registers. F is high from vStart to vEnd. L is high from hStart to hEnd. The object returns the current values of FOutReg, LOutReg, and DOutReg each time you call it.

This processing adds one cycle of delay to the control signals. The object passes through the pixel value after a matching delay cycle. For the complete code for the System object, see VHTtoCAMERALINKAdapter.m.

#### **Create Conversion Functions That Support HDL Code Generation**

Wrap the converter System objects in functions, similar to InvertImage, so you can generate HDL code for these algorithms.

```

function [ctrl,pixelOut] = CameraLinkToVisionHDL(F,L,D,pixel)

% CameraLink2VisionHDL : converts one cycle of CameraLink control signals

% to Vision HDL format, using a custom System object.

% Introduces two cycles of delay to both ctrl signals and pixel data.

persistent CL2VHT;

if isempty(CL2VHT)

CL2VHT = CAMERALINKtoVHT_Adapter();

end

[ctrl,pixelOut] = CL2VHT(F,L,D,pixel);

```

See CameraLinkToVisionHDL.m, and VisionHDLToCameraLink.m.

#### Write a Test Bench

To invert a Camera Link pixel stream using these components, write a test bench script that:

- **1** Preallocates output vectors to reduce simulation time

- 2 Converts the Camera Link control signals for each pixel to the Vision HDL Toolbox format

- **3** Calls the **Invert** function to flip each pixel value

- **4** Converts the control signals for that pixel back to the Camera Link format

```

[~,numPixelsPerFrame] = size(pixel);

pixOut = zeros(numPixelsPerFrame,1,'uint8');

pixel_d = zeros(numPixelsPerFrame,1,'uint8');

pixOut_d = zeros(numPixelsPerFrame,1,'uint8');

DOut = false(numPixelsPerFrame,1);

FOut = false(numPixelsPerFrame,1);

LOut = false(numPixelsPerFrame,1);

ctrl = repmat(pixelcontrolstruct,numPixelsPerFrame,1);

ctrlOut = repmat(pixelcontrolstruct,numPixelsPerFrame,1);

for p = 1:numPixelsPerFrame

[pixel_d(p),ctrl(p)] = CameraLinkToVisionHDL(pixel(p),F(p),L(p),D(p));

[pixOut(p),ctrlOut(p)] = Invert(pixel_d(p),ctrl(p));

[pixOut_d(p),FOut(p),LOut(p),DOut(p)] = VisionHDLToCameraLink(pixOut(p),ctrlOut(p));

end

```

#### **View Results**

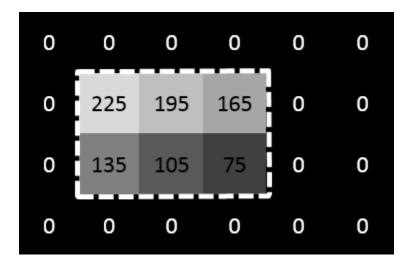

The resulting vectors represent this inverted 2-by-3, 8-bit grayscale frame. In the figure, the active image area is in the dashed rectangle, and the inactive pixels surround it. The pixels are labeled with their grayscale values.

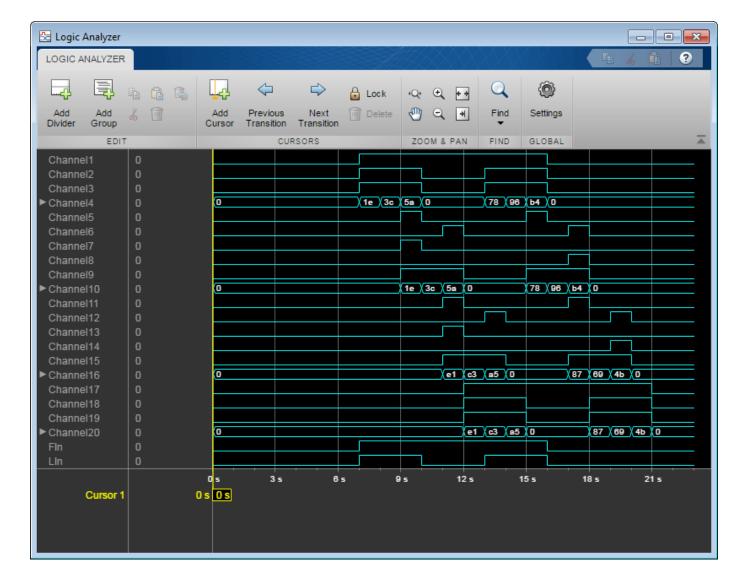

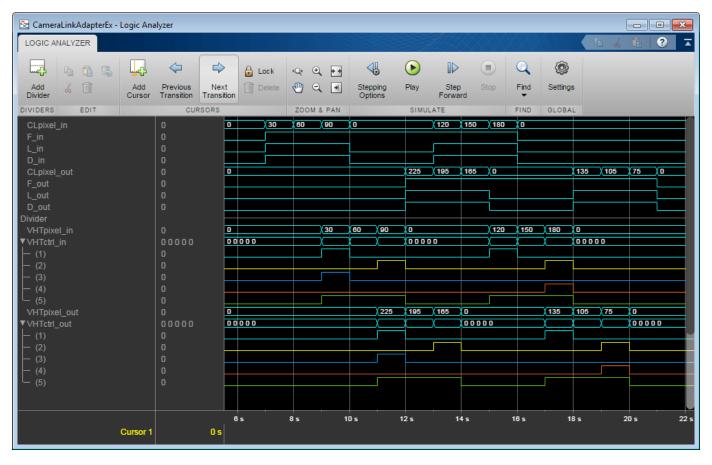

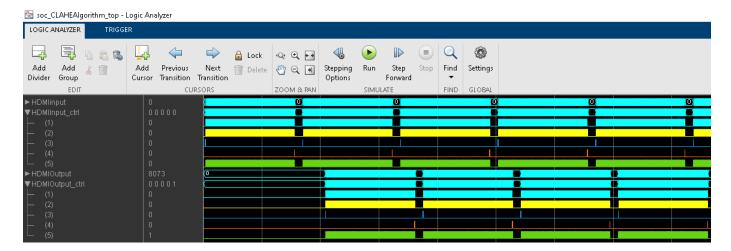

If you have a DSP System Toolbox $^{\text{TM}}$  license, you can view the vectors as signals over time using the Logic Analyzer. This waveform shows the pixelcontrol and Camera Link control signals, the starting pixel values, and the delayed pixel values after each operation.

#### **See Also**

pixelcontrolstruct|pixelcontrolsignals

#### **More About**

# **Integrate Vision HDL Blocks into Camera Link System**

This example shows how to design a Vision HDL Toolbox $^{\text{\tiny TM}}$  algorithm for integration into an existing system that uses the Camera Link $^{\text{\tiny RM}}$  signal protocol.

Vision HDL Toolbox blocks use a custom streaming video format. If you integrate Vision HDL Toolbox algorithms into existing design and verification code that operates in a different streaming video format, you must convert the control signals at the boundaries. The example uses custom System objects to convert the control signals between the Camera Link format and the Vision HDL Toolbox pixelcontrol format. The model imports the System objects to Simulink® by using the MATLAB® System block.

#### Structure of the Model

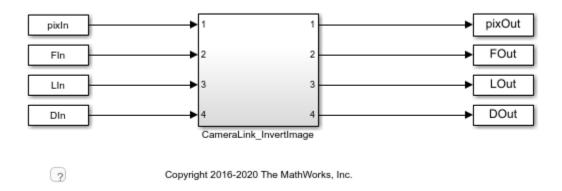

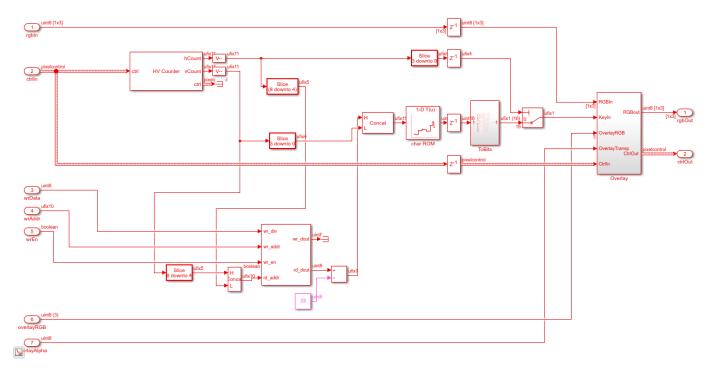

This model imports pixel data and control signals in the Camera Link format from the MATLAB workspace. The CameraLink\_InvertImage subsystem is designed for integration into existing systems that use Camera Link protocol. The CameraLink\_InvertImage subsystem converts the control signals from the Camera Link format to the pixelcontrol format, modifies the pixel data using the Lookup Table block, and then converts the control signals back to the Camera Link format. The model exports the resulting data and control signals to workspace variables.

#### Structure of the Subsystem

The CameraLink2VHT and VHT2CameraLink blocks are MATLAB System blocks that point to custom System objects. The objects convert between Camera Link signals and the pixelcontrol format used by Vision HDL Toolbox blocks and objects.

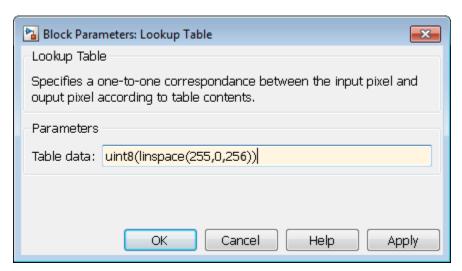

You can put any combination of Vision HDL Toolbox blocks into the middle of the subsystem. This example uses an inversion Lookup Table.

You can generate HDL from this subsystem.

blocks do not need to know the size/format of the frame

#### Import Data in Camera Link Format

Camera Link consists of three control signals: F indicates the valid frame, L indicates each valid line, and D indicates each valid pixel. For this example, the input data and control signals are defined in the InitFcn callback. The vectors describe this 2-by-3, 8-bit grayscale frame. In the figure, the active image area is in the dashed rectangle, and the inactive pixels surround it. The pixels are labeled with their grayscale values.

#### **Convert Camera Link Control Signals to pixelcontrol Format**

Write a custom System object to convert Camera Link signals to the Vision HDL Toolbox format. This example uses the object designed in the "Convert Camera Control Signals to pixelcontrol Format" on page 1-24 example.

The object converts the control signals, and then creates a structure that contains the new control signals. When the object is included in a MATLAB System block, the block translates this structure into the bus format expected by Vision HDL Toolbox blocks. For the complete code for the System object, see CAMERALINKtoVHT Adapter.m.

Create a MATLAB System block and point it to the System object.

### **Design Vision HDL Toolbox Algorithm**

Select Vision HDL Toolbox blocks to process the video stream. These blocks accept and return a scalar pixel value and a pixelcontrol bus that contains the associated control signals. This standard interface makes it easy to connect blocks from the Vision HDL Toolbox libraries together.

This example uses the Lookup Table block to invert each pixel in the test image. Set the table data to the reverse of the uint8 grayscale color space.

### **Convert pixelcontrol to Camera Link**

Write a custom System object to convert Vision HDL Toolbox signals back to the Camera Link format. This example uses the object designed in the "Convert Camera Control Signals to pixelcontrol Format" on page 1-24 example.

The object accepts a structure of control signals. When you include the object in a MATLAB System block, the block translates the input pixelcontrol bus into this structure. Then it computes the equivalent Camera Link signals. For the complete code for the System object, see VHTtoCAMERALINKAdapter.m.

Create a second MATLAB System block and point it to the System object.

#### **View Results**

Run the simulation. The resulting vectors represent this inverted 2-by-3, 8-bit grayscale frame. In the figure, the active image area is in the dashed rectangle, and the inactive pixels surround it. The pixels are labeled with their grayscale values.

If you have a DSP System Toolbox™ license, you can view the signals over time using the Logic Analyzer. Select all the signals in the CameraLink\_InvertImage subsystem for streaming, and open the Logic Analyzer. This waveform shows the input and output Camera Link control signals and pixel values at the top, and the input and output of the Lookup Table block in pixelcontrol format at the bottom. The pixelcontrol busses are expanded to observe the boolean control signals.

For more info on observing waveforms in Simulink, see "Inspect and Measure Transitions Using the Logic Analyzer" (DSP System Toolbox).

#### **Generate HDL Code for Subsystem**

To generate HDL code you must have an HDL Coder<sup>™</sup> license.

To generate the HDL code, use the following command.

makehdl('CameraLinkAdapterEx/CameraLink\_InvertImage')

You can now simulate and synthesize these HDL files along with your existing Camera Link system.

# **See Also**

## **More About**

• "Streaming Pixel Interface" on page 1-2

# **HDL-Optimized Algorithm Design**

# **Configure Blanking Intervals**

Streaming video protocols have two blanking intervals: horizontal and vertical. The horizontal blanking interval is the period of inactive cycles between the end of one line and the beginning of the next line. The vertical blanking interval is the period of inactive lines between the end of a frame and the beginning of the next frame.

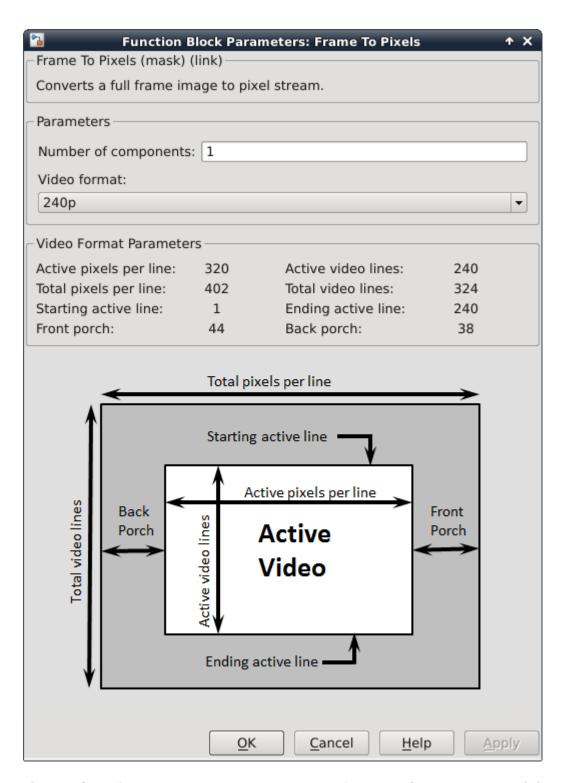

In this frame diagram, the blue shaded areas to the left and right of the active frame indicate the horizontal blanking interval. The orange shaded areas above and below the active frame indicate the vertical blanking interval.

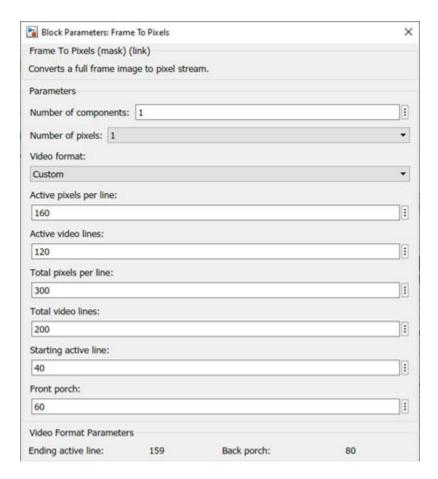

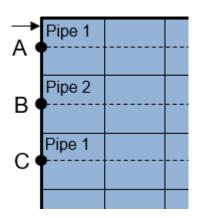

In the Frame To Pixels block, the horizontal blanking interval is equal to **Total pixels per line** – **Active pixels per line** or, equivalently, **Front porch** + **Back porch**. The vertical blanking interval is equal to **Total video lines** – **Active video lines** or, equivalently, **Starting active line** + **Ending active line** – **Active video lines**.

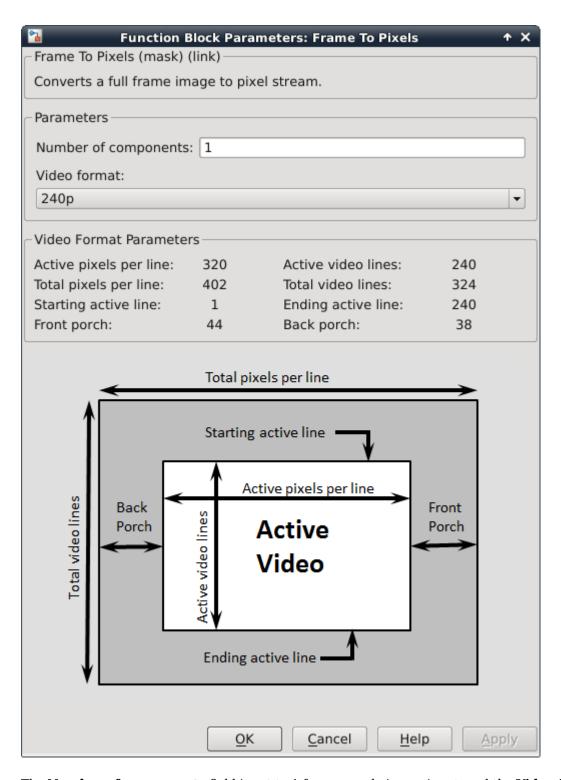

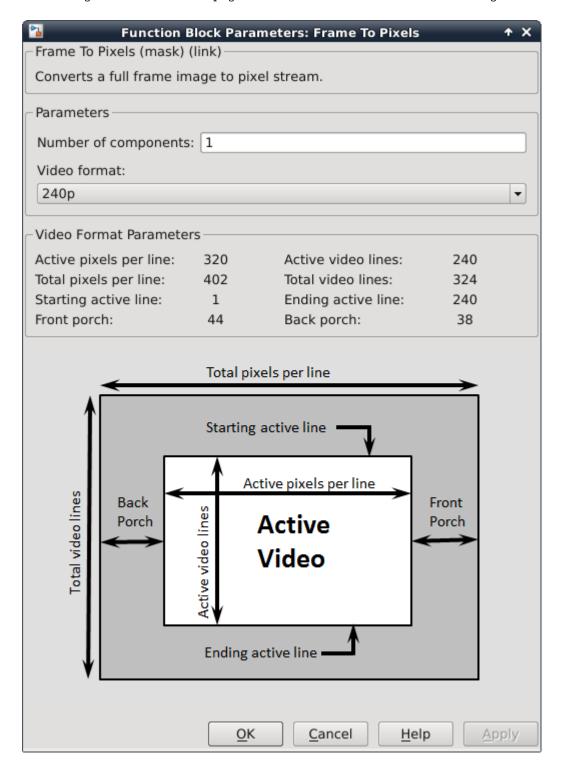

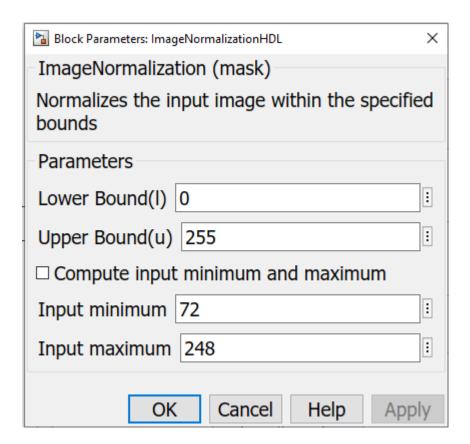

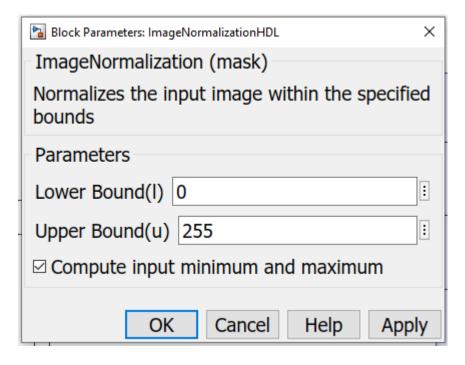

For example, the Frame To Pixels block whose parameters are shown in this image has a horizontal blanking interval of 140 pixels and a vertical blanking interval of 80 lines.

A streaming video format must have a long enough blanking interval so that the operation on the previous line or frame completes before the next line or frame starts. An inadequate horizontal or vertical blanking interval results in corrupted output frames. Standard streaming video formats use a horizontal blanking interval of about 25% of the line width. This interval is much larger than the delay of a typical operation. However, when you use a custom video format, you must include blanking intervals that accommodate the length of the operations in your design.

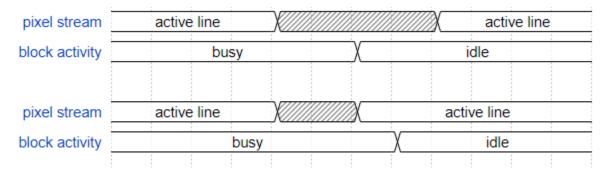

In these waveform diagrams, the top signal shows the state of the pixel stream for two lines of a frame. The shaded area represents the horizontal blanking interval between lines. The bottom signal shows the state of the block performing an operation on the pixel stream. The busy state indicates when the block is processing a line, and the idle state indicates when the block is available to start working on a new line. The first pair of signals shows a scenario where the block finishes working on the first active line before the second line begins. This blanking interval is long enough to ensure correct output frames, because the block is available to start work on the second line when it arrives. The second pair of signals shows a scenario where the block is still working on the first active line when the second line begins. The output of the block is corrupted in the second case, because the block misses the beginning of the second line.

The time an operation takes to complete after the end of the line is often dependent on the kernel size of the operation. For instance, algorithms that use line buffers and apply padding pixels to the edge of the frame require at least Kw cycles between lines, where Kw is the width of the kernel. An algorithm might also have pipeline delays from the kernel operation after the buffer. These delays can be related or unrelated to the kernel size, and can be greater or smaller than the line buffer delays. The processing time of each operation depends on the line buffer pipelining and on the kernel operation pipelining. The blanking interval must be long enough to accommodate the longer of these two delays. When you use multiple blocks in a processing chain, the blanking interval must accommodate the block with the longest delay.

The recommended minimum horizontal blanking interval is  $2 \times Kw$  when using padding or 12 cycles when you set the **Padding method** parameter to None. This interval includes some margin for longer kernel processing times on top of the line buffer delay.

The recommended vertical blanking interval is at least the height of the kernel, *Kh* lines. The line buffer requires this interval whether or not the operation uses padding.

**Note** When you use a pixel streaming block inside an Enabled Subsystem, the enable signal pattern must maintain the timing of the pixel stream, including the minimum blanking intervals. You may need to extend the blanking intervals to accommodate for cycles when the enable is low.

# **Troubleshoot Blanking Interval Problems**

When the blanking interval is too small, you might see:

- · Blank output frames

- Partial output frames

- Corrupted pixel stream control signal patterns (for instance, missing vEnd or hEnd signals, or duplicate End or Start signals)

- That the algorithm works with continuous valid input pixels on each line, but not when gaps exist between valid pixels in a line

- That the algorithm works in Simulink but fails in HDL simulation

Vision HDL Toolbox library blocks model hardware pipeline stages as a latency applied at the output. In the corresponding HDL implementations, the pipeline stages are distributed across the calculation. This difference means that for a given cycle, a block can be in a busy state in HDL simulation but appear idle in Simulink. When the blanking period is too short, this difference can cause the generated HDL test bench to show mismatches between Simulink and HDL signals, especially on the output control signals.

If you see any of these symptoms, increase your horizontal and vertical blanking intervals to 25% of the active frame dimensions and rerun the simulation. If this step confirms that a too-small blanking interval is causing your symptoms, you can fine tune the intervals.

One way to diagnose blanking interval problems in Simulink is to use the Measure Timing block to observe the dimensions of the pixel stream before and after your operation. Inadequate blanking intervals cause the block to corrupt the control signals. In these cases, the output frames show different dimensions than the input frames.

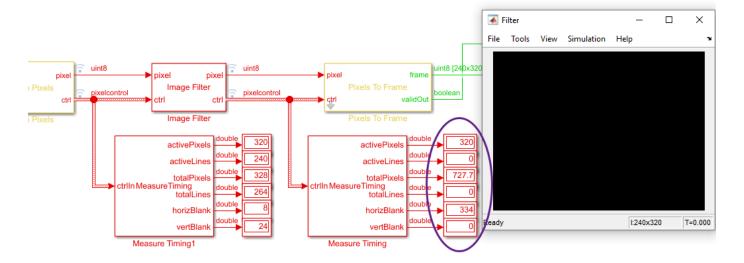

This model shows an Image Filter block configured with a 12-by-12 filter kernel and edge padding enabled. The pixel stream format is a custom format that has only 8 horizontal blanking pixels, as shown by the Measure Timing block on the input stream. Because the horizontal blanking interval is smaller than the kernel width, the output frame is blank. The Measure Timing block on the output of the filter shows corruption of the format.

You can also see the corruption by looking at the output control signals in the **Logic Analyzer** app. The waveform shows the input and output signals of the Image Filter block. The red arrows indicate missing hStart signals and a different pattern on the output valid signal from the block.

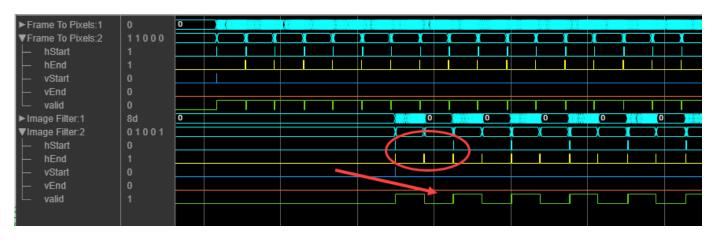

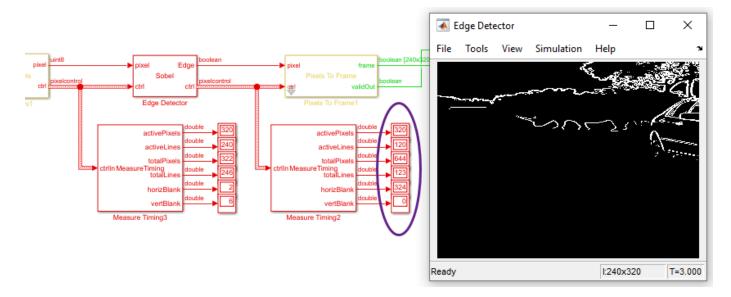

This model shows an Edge Detector block configured to use the 3-by-3 Sobel filter kernel and with edge padding enabled. This pixel stream format has only two horizontal blanking pixels, as shown by

the Measure Timing block on the input stream. In this case, the output frame includes only every second line. The Measure Timing block on the output of the filter shows the corruption of the format.

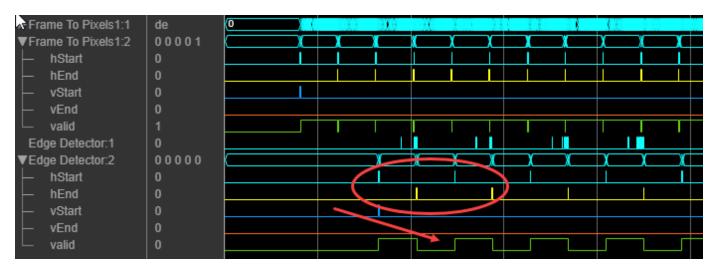

You can also see the corruption by looking at the output control signals in the **Logic Analyzer** app. The waveform shows the input and output signals of the Edge Detector block. The red circle indicates missing hStart and hEnd signals, and the red arrow indicates a different pattern on the output valid signal from the block.

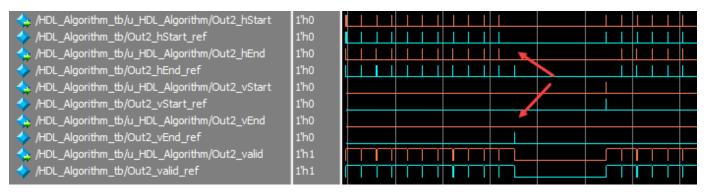

If you modify the input format to have a horizontal blanking interval of 3 pixels, this model returns the correct output frames in Simulink. However, when you run the generated HDL test bench, the test bench reports mismatches between the signals captured in Simulink and the signal behavior in HDL. This image of the test bench log highlights the mismatch in the output hEnd and vEnd signals.

```

# ERROR in Out2 hStart at time

781920 : Expected '0' Actual '1'

ERROR in Outl at time

781920 : Expected '0' Actual '1'

# ERROR in Out2 valid at time

781920 : Expected '0' Actual '1'

# ERROR in Out2 hStart at time

781930 : Expected '1' Actual '0'

ERROR in Outl at time

784750 : Expected '1' Actual '0'

ERROR in Outl at time

784990 : Expected '0' Actual '1'

ERROR in Outl at time

785100 : Expected '1' Actual '0'

ERROR in Out2 valid at time

785100 : Expected '1' Actual '0'

# ERROR in Out2 valid at time

785110 : Expected '1' Actual '0'

# ERROR

785110 : Expected '1' Actual '0'

ERROR in Out2 vEnd at time

785120 : Expected '1' Actual '0'

ERROR in Out2 hEnd at time

785120 : Expected '1' Actual '0'

# ERROR in outl at time

785120 : Expected '1' Actual '0'

# ERROR in Out2 valid at time

785120 : Expected '1' Actual '0'

```

This waveform from the simulation of the HDL test bench shows that the hEnd and vEnd signals at the end of the first frame are missing. The blue signals are the expected output as captured from the Simulink simulation. The red signals are the output of the algorithm in the HDL simulation. The red arrows indicate where the expected control signal pulses are missing.

To fix the Image Filter model and the Edge Detector model, set the horizontal blanking interval to at least  $2 \times Kw$  pixels, where Kw is the width of the filter kernel. For the Image Filter model, set this value to at least 24 pixels. For the Edge Detector model, set this value to at least 8 pixels.

# See Also

Frame To Pixels | Measure Timing

### **More About**

• "Streaming Pixel Interface" on page 1-2

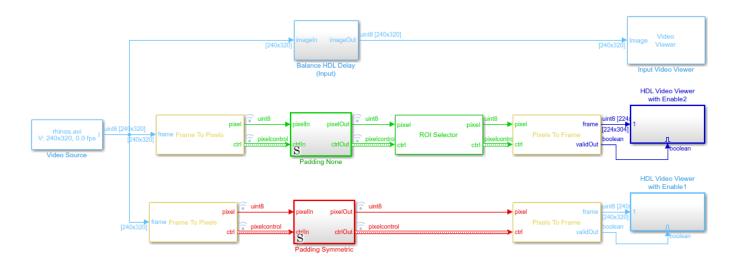

# **Edge Padding**

To perform a kernel-based operation such as filtering on a pixel at the edge of a frame, Vision HDL Toolbox algorithms pad the edges of the frame with extra pixels. These padding pixels are used for internal calculation only. The output frame has the same dimensions as the input frame. The padding operation assigns a pattern of pixel values to the inactive pixels around a frame. Vision HDL Toolbox algorithms provide padding by constant value, replication, or symmetry.

Some blocks and System objects also support opting out of setting the padding pixel values. This option reduces the hardware resources used by the block and the blanking required between frames but affects the accuracy of the output pixels at the edges of the frame.

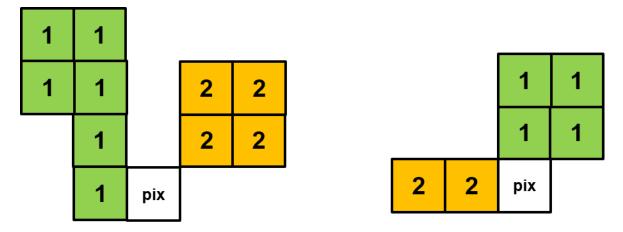

The diagrams show the top-left corner of a frame, with padding added to accommodate a 5-by-5 filter kernel. When computing the filtered value for the top-left active pixel, the algorithm requires two rows and two columns of padding. The edge of the active image is indicated by the double line.

| Type of Padding                                                                                     | Description                                                                                                                                                                                                       | Diagram |                                                                                                  |   |     |   |    |     |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------|---|-----|---|----|-----|

| Constant  Each added pix On some block specify the cor representing b some video sta number, such a | Each added pixel is assigned the same value. On some blocks and System objects you can specify the constant value. The value 0, representing black, is a reserved value in some video standards. Choosing a small | valu    | In the diagram, C is the constant value assigned to the inactive pixels around the active frame. |   |     |   |    |     |

|                                                                                                     | number, such as 16, as a near-black padding value, is common.                                                                                                                                                     |         | С                                                                                                | С | С   |   | С  | С   |

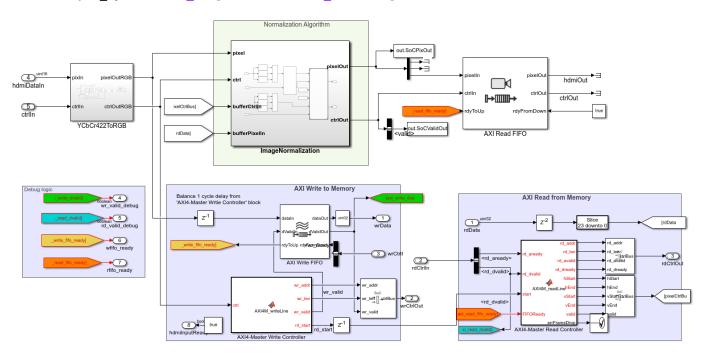

|                                                                                                     |                                                                                                                                                                                                                   |         | С                                                                                                | С | С   |   | С  | С   |